Summary of Contents for Cronologic Ndigo5G-8

- Page 1 Revision 1.0.8 as of 2018-11-19 Firmware 2 (build 4865), Driver v1.3.0 cronologic GmbH & Co. KG Ndigo5G-8 Ndigo5G-10 User Guide cronologic...

-

Page 4: Table Of Contents

Contents 1 Introduction 1.1 Features ......... 2 Hardware 2.1 Installing the Board . - Page 5 3.6 Other Functions ........3.6.1 LED control .

-

Page 6: Introduction

1 Introduction The Ndigo5G is a digitizer and transient recorder designed to sample relatively shorts pulses in rapid repetition. It produces a stream of output packets, each containing data from a single trigger event together with a timestamp. 1.1 Features ˆ... -

Page 8: Hardware

For more details, please refer to the Ndigo Crate user guide. In applications that use only a few Ndigo boards installed directly inside a PC, termination PCBs available from cronologic can be used. Ndigo5G’s standard device driver can be used to read out all boards and acquire data. For more complex scenarios, using the cronoSync-library, which is part of cronoTools, is recom- mended. -

Page 9: Ndigo5G External Inputs And Connectors

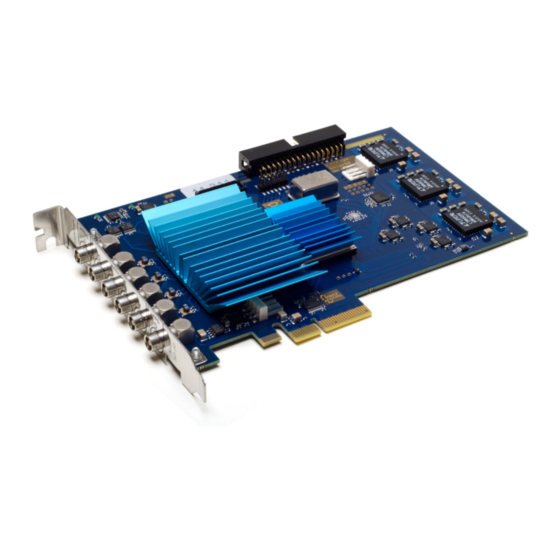

C2 is used as a bus interface between multiple Ndigo boards distributing clock, trigger and sync signals. Proper termination must be placed at both ends of the bus interconnection ribbon cable. Figure 2.2: Input connectors of an Ndigo5G located on the PCI bracket. cronologic GmbH & Co. KG Ndigo5G User Guide... -

Page 10: Analog Inputs

DC baseline to one end of the ADC range, the input range can be used fully, providing the maximum dynamic range. The analog offset can be set between 0, 25V . cronologic GmbH & Co. KG Ndigo5G User Guide... -

Page 11: Digital Inputs

The function ndigo process tdc packet() can be used to replace the coarse timestamp with the precise timestamp. This function is described in section on page 38. TDC pulses must have a minimum duration of 3.3ns. The dead-time of the TDC is 32ns. cronologic GmbH & Co. KG Ndigo5G User Guide... -

Page 12: Extension Card

LEMO00: CH1 BUS1 = EXT1 Sync Cable 1 BUS1 = EXT1 LEMO00: CH8 BUS2 = EXT2 Sync Cable 2 BUS2 = EXT2 LEMO00: CH9 BUS3 = EXT3 Sync Cable 3 BUS3 = EXT3 cronologic GmbH & Co. KG Ndigo5G User Guide... -

Page 13: Ndigo5G Functionality

During interleaving, the Ndigo5G firmware reorders and groups the data into a linear sample stream. The process is fully transparent. For users, the only difference is that a 3.2ns cycle can contain 4, 8 or 16 samples, depending on mode. cronologic GmbH & Co. KG Ndigo5G User Guide... - Page 14 1.25 Gsps 1.25 Gsps 1.25 Gsps 1.25 Gsps In-phase Inverted 1.25 GHz 1.25 GHz AAI,,AAIN,or,BAI,BAIN,or,CAI ,,CAIN,or,DAI ,,DAIN Figure 2.9: ADCs in 1 channel mode A, B, C or D interleaved for 5Gsps. cronologic GmbH & Co. KG Ndigo5G User Guide...

-

Page 15: Zero Suppression

PC. 2.4.3 Trigger Blocks Ndigo5G-10 and Ndigo5G-8 record analog waveforms using zero suppression. Whenever a rel- evant waveform is detected, data is written to an internal FIFO memory. Each ADC channel has one trigger block determining whether data is written to the FIFO. The parameters are set in Structure ndigo trigger block(See chapter 3.4.3... - Page 16 This procedure reduces PCIe bus load even further (Figure 2.20). total length = 19 precursor = 6 length = 12 Figure 2.11: Parameters for edge triggering cronologic GmbH & Co. KG Ndigo5G User Guide...

- Page 17 Figure 2.13: Triggering in 4 channel mode at 4 samples per clock cycle. total length = 4 precursor = 1 length = 2 3200 ps Figure 2.14: Triggering in 2 channel mode at 8 samples per clock cycle. cronologic GmbH & Co. KG Ndigo5G User Guide...

- Page 18 Figure 2.16: From the ADC inputs, a trigger unit creates an input flag for the trigger matrix. Each digitizer channel (A, B, C, D) has two trigger units. input rising edge Figure 2.17: The digital inputs Trigger, GATE, BUS0, BUS1, BUS2 and BUS3 have simpler trigger units. cronologic GmbH & Co. KG Ndigo5G User Guide...

- Page 19 GATE input or the sync cable can be combined to create a trigger input for each trigger block. The four gate signals can be used to suppress triggers during certain time frames. cronologic GmbH & Co. KG Ndigo5G User Guide...

-

Page 20: Gating Blocks

The parameters of a gating block are set in Structure ndigo gating block described on page Figure 2.21 shows the functionality of the gate timing and delay unit. Active gate time is marked in green. cronologic GmbH & Co. KG Ndigo5G User Guide... - Page 21 (see fig. 2.22): a falling level trigger with an upper threshold and a rising level trigger with a lower threshold. cronologic GmbH & Co. KG Ndigo5G User Guide...

- Page 22 . t r i g g e r [ NDIGO TRIGGER A1 ] . r i s i n g = 1 ; c o n f i g . t r i g g e r [ NDIGO TRIGGER A1 ] . t h r e s h o l d = 10000; cronologic GmbH & Co. KG Ndigo5G User Guide...

-

Page 23: Auto Triggering Function Generator

The packets have a fixed length of 16 bytes. The format is described on page 41. The length field of the packet contains a 32 bit pattern that contains the levels of all trigger sources at the cronologic GmbH & Co. KG Ndigo5G User Guide... -

Page 24: Data Lookup Table

(LUT) which needs to be provided by the user. This is done by defining the corresponding function as a custom lut-member of the ndigo configuration structure. Please feel free to contact cronologic if you plan the use this feature. The onboard INL correction is applied prior to mapping the LUT values. -

Page 25: Calibration Procedure

Only Ndigo5G boards may be set as masters. Therefore, a Ndigo250M board only needs to be calibrated as a slave. 6. After finding all delay values, write the values to the on-board flash PROMs by pressing “Flash All!”. cronologic GmbH & Co. KG Ndigo5G User Guide... - Page 26 Figure 2.26: Histogram for the case the delay value for the board is set correctly. Please note: the lower panel might differ from board to board, with the “step” being at a different position. cronologic GmbH & Co. KG Ndigo5G User Guide...

-

Page 27: Synchronizing A Ndgio5G And An Hptdc8-Pci

Ndigo5G device driver. CronoSync offers an easy group-based access to the data recorded and handles the synchronization of all cronologic data ac-quisition devices used. A detailed description of cronoTools and cronoSync can be found in the cronoTools user guide. -

Page 28: Calibrating The Tdc

Offset by one. Repeat increment/decrement until First Bin is in the range of 4 to 16. Depending on the firmware revision the Input Offset value for a successful calibration may be in the range of 6 – 10 or 28 – 32. cronologic GmbH & Co. KG Ndigo5G User Guide... - Page 29 ˆ at least 10,000 events have been captured ˆ a valid serial number is set. Important note: If the application reports an error check if the input pulse is within speci- fication. cronologic GmbH & Co. KG Ndigo5G User Guide...

-

Page 30: Driver Programming Api

3 Driver Programming API The API is a DLL with C linkage. The functions provided by the DLL are declared in Ndigo interface.h. 3.1 Constants #define NDIGO CHANNEL COUNT 4 The number of analog input channels. #define NDIGO GATE COUNT 4 The number of gating blocks. - Page 31 Set to 0. Can be used to activate future device variants such as different base frequencies. device type Initialized by ndigo get default init parameters(). Must be left unchanged. #define CRONO DEVICE HPTDC 0 #define CRONO DEVICE NDIGO5G 1 #define CRONO DEVICE NDIGO250M 2 cronologic GmbH & Co. KG Ndigo5G User Guide...

-

Page 32: Status Information

Firmware revision of the FPGA configuration. This increments only when there is a functional change. board revision 0 for experimental prototypes labeled “Rev. 1” 2 for the version produced until 2010 labeled “Rev. 2”‘ cronologic GmbH & Co. KG Ndigo5G User Guide... - Page 33 Bit 3 = 1 signifies a special version of the board 0xA is Ndigo1250M-12 single ended with digital trigger 0x8 is Ndigo5G-8 single ended with digital trigger For Board revision 3 the following assignments are valid: Bit 2 determines the input connectors (0 = single ended, 1 = differential).

-

Page 34: Structure Ndigo Param Info

Set to 0 for all versions up to first release. adc rpm Speed of the ADC fan. Reports 0 if no fan is present. cronologic GmbH & Co. KG Ndigo5G User Guide... -

Page 35: Structure Ndigo Slow Info

*device, ndigo configuration *config) ndigo get current configuration(ndigo device *device, ndigo configuration *config) cronologic GmbH & Co. KG Ndigo5G User Guide... -

Page 36: Structure Ndigo Configuration

The -8, -10 and -12 versions currently supports 1GHz and 3GHz bandwidth, the -8AQ version supports 2GHz, 1.5GHz, 600MHz and 500 MHz. ndigo bool t reserved ndigo bool t tdc enabled cronologic GmbH & Co. KG Ndigo5G User Guide... - Page 37 A structure describing the routing of the 4 digital channels of the Ndigo extension board to the trigger matrix. drive bus[4] Enable output drive for each of the four external sync lines. Each integer represents a bitmask cronologic GmbH & Co. KG Ndigo5G User Guide...

-

Page 38: Structure Ndigo Trigger

Sets the threshold for the trigger block within the range of the ADC data of -32768 and +32768. For trigger indices NDIGO TRIGGER TDC to NDIGO TRIGGER BUS3 PE the threshold is ig- nored. cronologic GmbH & Co. KG Ndigo5G User Guide... -

Page 39: Structure Ndigo Trigger Block

The length setting is ignored for the timestamp channel. sources A bit mask with a bit set for all trigger sources that can trigger this channel. cronologic GmbH & Co. KG Ndigo5G User Guide... - Page 40 FIFO was full. As a measure for the packet length the gatelength set by the user is used. The on-board algorithm checks the free FIFO cronologic GmbH & Co. KG Ndigo5G User Guide...

-

Page 41: Structure Ndigo Gating Block

A bit mask with a bit set for all trigger sources that can trigger this channel. The gates cannot use the additional digital trigger sources NDIGO TRIGGER SOURCE TDC PE to NDIGO TRIGGER SOURCE BUS3 PE. cronologic GmbH & Co. KG Ndigo5G User Guide... -

Page 42: Structure Ndigo Extension Block

*device) ndigo pause capture(ndigo device *device) ndigo continue capture(ndigo device *device) Call this to resume data acquisition after a call to ndigo pause capture. ndigo stop capture(ndigo device *device) cronologic GmbH & Co. KG Ndigo5G User Guide... -

Page 43: Readout

This means that used channels are lit green, activity is shown as yellow on overflow is shown as red. ndigo set led color(ndigo device *device, led, unsigned short unsigned short cronologic GmbH & Co. KG Ndigo5G User Guide... - Page 44 Set the LED to the selected color. No automatic updates are performed. ndigo set led automode(ndigo device *device, led) Let the selected LED be controlled by hardware. cronologic GmbH & Co. KG Ndigo5G User Guide...

- Page 45 GmbH & Co. KG Ndigo5G User Guide...

-

Page 46: Packet Format

4 Packet Format 4.0.1 Output Structure ndigo packet unsigned char channel 0 to 3 for the ADC input channels, 4 for the TDC, 5 for the timestamp channel. unsigned char card Identifies the source card in case there are multiple boards present. Defaults to 0 if no value is assigned to the parameter board id in Structure ndigo init parameters or set via int ndigo set board id(ndigo device *device, int board id). - Page 47 Sample data. For the Ndigo5G each 64 bit word contains four 16 bit signed words from the ADC. The user can cast the array to short* to directly operate on the sample data. cronologic GmbH & Co. KG Ndigo5G User Guide...

-

Page 48: Example

5 C Example #i n c l u d e ” N d i g o i n t e r f a c e . h” #i n c l u d e <s t d i o . h> #i n c l u d e <... - Page 49 = n e x t p a c k e t ; c o u n t ++; n d i g o c l o s e ( ndgo ) ; r e t u r n 0 ; cronologic GmbH & Co. KG Ndigo5G User Guide...

-

Page 50: Technical Data

6 Technical Data Input Passband: 4.5MHz to 3000MHz. Power Requirements: 25W Mechanical Dimensions: 170mm 106mm Throughput: 800MByte/s on PCIe x4 6.1 Digitizer Characteristics Each board ist tested against the values listed in the ‘Min’ column. ‘Typical’ is the mean value of the first 10 boards produced. -

Page 51: 4-Channel-Mode (1.25 Gsps)

31 C 6.2.3 Environmental Conditions for Storage The board shall be stored between operation under the following conditions: Symbol Parameter Typical Units ambient temperature relative humidity at 31 C non condensing cronologic GmbH & Co. KG Ndigo5G User Guide... -

Page 52: Power Supply

Analog offset -0,25 0.25 6.3 Information Required by DIN EN 61010-1 6.3.1 Manufacturer The Ndigo5G is a product of: cronologic GmbH & Co. KG Jahnstraße 49 60318 Frankfurt HRA 42869 beim Amtsgericht Frankfurt/M VAT-ID: DE235184378 cronologic GmbH & Co. KG... -

Page 53: Intended Use And System Integration

Nutzung”. The last owner of a Ndigo5G must recycle it or treat the board in com- pliance with § 11 and § 12 of the German ElektroG or return it to cronologic at the address listed cronologic GmbH & Co. KG... - Page 54 47. cronologic GmbH & Co. KG Ndigo5G User Guide...

Need help?

Do you have a question about the Ndigo5G-8 and is the answer not in the manual?

Questions and answers