Table of Contents

Advertisement

Quick Links

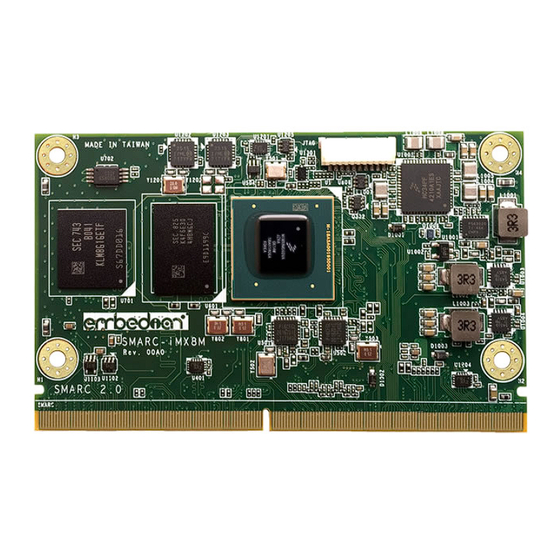

Embedian, Inc.

(SMARC 2.0 Specification Compliant)

SMARC-iMX8M Computer on Module User's Manual v.1.0

SMARC Computer on Module

NXP/Freescale i.MX8M Cortex A53 and Cortex M4

24bits dual‐channel LVDS

HDMI 2.0a/DP

4 x COM Ports

1 x SDHC

1 x USB Host 2.0, 1 x USB 2.0 OTG, 2 x USB3.0

1 x 10/100/1000M Gigabit Ethernet

2 x CAN Bus, 2 x SPIs, 5 x I2Cs, 12‐bit GPIOs

2 x PCIe x1 Gen. 2.1, 2 x MIPI_CSI

SMARC‐iMX8M

Dual, Quad and Quad Lite Cores

1

Advertisement

Table of Contents

Summary of Contents for Embedian SMARC-iMX8M Series

- Page 1 Embedian, Inc. SMARC Computer on Module NXP/Freescale i.MX8M Cortex A53 and Cortex M4 24bits dual‐channel LVDS HDMI 2.0a/DP 4 x COM Ports 1 x SDHC 1 x USB Host 2.0, 1 x USB 2.0 OTG, 2 x USB3.0 1 x 10/100/1000M Gigabit Ethernet 2 x CAN Bus, 2 x SPIs, 5 x I2Cs, 12‐bit GPIOs 2 x PCIe x1 Gen. 2.1, 2 x MIPI_CSI SMARC‐iMX8M Dual, Quad and Quad Lite Cores (SMARC 2.0 Specification Compliant) SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 2 Embedian, Inc. SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 3 Embedian, Inc. Revision History Revision Date Changes from Previous Revision 1.0 2018/08/28 Initial Release SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 4 Android is a registered trademark of Google Linux is a registered trademark of Linus Torvalds. WinCE is a registered trademark of Microsoft NXP is a registered trademark of NXP All other products and trademarks mentioned in this manual are trademarks of their respective owners. Standards EMBEDIAN is ISO 9001:2008 and ISO14001‐certified manufacturer. SMARC is an SGET standard for ARM computer on module. Warranty This EMBEDIAN product is warranted against defects in material and workmanship for the warranty period from the date of shipment. During the warranty period, EMBEDIAN will at its discretion, decide to repair or replace defective products. SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 5 The warranty does not apply to defects resulting from improper or inadequate maintenance or handling by the buyer, unauthorized modification or misuse, operation outside of the product’s environmental specifications or improper installation or maintenance. EMBEDIAN will not be responsible for any defects or damages to other products not supplied by EMBEDIAN that are caused by a faulty EMBEDIAN product. Technical Support ...

-

Page 6: Table Of Contents

Embedian, Inc. Table of Contents CHAPTER 1 INTRODUCTION ........................10 1.1 FEATURES AND FUNCTIONALITY ....................... 11 1.2 MODULE VARIANT ..........................13 1.3 BLOCK DIAGRAM ..........................14 1.4 SOFTWARE SUPPORT / HARDWARE ABSTRACTION ................15 1.5 DOCUMENT AND STANDARD REFERENCES ..................15 CHAPTER 2 SPECIFICATIONS ........................20 2.1 SMARC‐IMX8M GENERAL FUNCTIONS ..................... 20 2.2 SMARC‐IMX8M DEBUG ........................97 ... - Page 7 Embedian, Inc. Using this Manual This guide provides information about the Embedian SMARC‐iMX8M for NXP i.MX8M embedded SMARC core module family. Conventions used in this guide This table describes the typographic conventions used in this guide: This Convention Is used for Italic type Emphasis, new terms, variables, and document titles. monospaced type Filenames, pathnames, and code examples. Embedian Information Document Updates Please always check the product specific section on the Embedian support website at www.embedian.com/ for the most current revision of this document. Contact Information For more information about your Embedian products, or for customer service and technical support, contact Embedian directly. To contact Embedian by Use Mail Embedian, Inc. 9F‐4. 432 Keelung Rd. Sec. 1, Taipei 11051, Taiwan World Wide Web http://www.embedian.com/ Telephone + 886 2 2722 3291 SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 8 Embedian, Inc. Additional Resources Please also refer to the most recent NXP i.MX8M processor reference manual and related documentation for additional information. SMARC-iMX8M Computer on Module User’s Manual v.1.0...

-

Page 9: Chapter 1 Introduction

Embedian, Inc. Introduction This Chapter gives background information on the SMARC‐iMX8M Section include: Features and Functionality Module Variant Block diagram Software Support / Hardware Abstraction Module Variant Document and Standard References SMARC-iMX8M Computer on Module User’s Manual v.1.0... - Page 10 18‐bit/24‐bit LVDS LCD, Gigabit Ethernet, HDMI/DP, SDHC, USB 2.0, USB USB 3.0, UARTs, CAN bus, PCIe and many peripheral interfaces in a cost effective, low power, miniature package. Embedian’s SMARC‐iMX8M thin and robust design makes it an ideal building block for ...

-

Page 11: Features And Functionality

Embedian, Inc. 9 , Ubuntu 16.04 and Android Oreo 8.1 allow immediate and professional embedded product development with dramatically reduced design risk and time‐to‐market. 1.1 Features and Functionality The SMARC‐iMX8M module is based on the i.MX8M processor with dual, quad lite, and quad core from NXP. This processor offers a high number of interfaces. The module has the following features: SMARC 2.0 compliant in an 82mm x 50mm form factor. Processor: NXP i.MX8M ARM Cortex‐A53 and Cortex‐M4 up to 1.5GHz Memory: Onboard 8GB eMMC Flash Onboard 2GB or 4GB LPDDR4 Networking: 1 x 10/100/1000 Mbps Ethernet Display: ... - Page 12 Embedian, Inc. Thermal: Commercial Temperature: 0 C ~ 80 Industrial Temperature: ‐40 ~85 Power Supply 3V to 5.25V 1.8V module IO support (SMARC 2.0 compliant) SMARC-iMX8M Computer on Module User’s Manual v.1.0...

-

Page 13: Module Variant

Embedian, Inc. 1.2 Module Variant The SMARC‐iMX8M module is available with various options based on processors in this family from NXP, LPDDR4 memory configuration, and operating temperature ranges. “D” (dual core, CPU running up to 2 x 1.5GHz) “L” (quad lite core, CPU running up to 4 x 1.5GHz) “Q” (quad core, CPU running up to 4 x 1.5GHz) “2G” (2GB LPDDR4 memory) “4G” (4GB LPDDR4 memory) “I” -Industrial temperature (‐40 C~85 C for 2GB LPDDR4 a n d ‐ 3 0 C~85 for 4GB LPDDR4), CPU running up to 1.3GHz, support 2GB LPDDR4 only) ... -

Page 14: Block Diagram

Embedian, Inc. 1.3 Block Diagram The following diagram illustrates the system organization of the SMARC‐iMX8M. Arrows indicate direction of control and not necessarily signal flow. Figure 1: SMARC‐iMX8M Block Diagram Details for this diagram will be explained in the following chapters. SMARC-iMX8M Computer on Module User’s Manual v.1.0... -

Page 15: Software Support / Hardware Abstraction

Embedian, Inc. 1.4 Software Support / Hardware Abstraction The Embedian SMARC‐iMX8M Module is supported by Embedian BSPs (Board Support Package). The first SMARC‐iMX8M BSP targets Linux (Ubuntu 16.04 LTS, Debian 9, Yocto Build) and Android Oreo 8.1 support. BSPs for other operating systems are planned. Check with your Embedian contact for the latest BSPs. This manual goes into a lot of detail on I/O particulars – information is provided on exactly how the various SMARC edge fingers tie into the NXP i.MX8M SoC and to other Module hardware. This is provided for reference and context. Almost all of the I/O particulars are covered and abstracted in the BSP and it should generally not be necessary for users to deal with I/O at the register level. 1.5 Document and Standard References 1.5.1. External Industry Standard Documents eMMC (Embedded Multi‐Media Card) the eMMC electrical standard is defined by JEDEC JESD84‐B45 and the mechanical standard by JESD84‐C44 (www.jedec.org). The I2C Specification, Version 2.1, January 2000, Philips Semiconductor (now NXP) (www.nxp.com). I2S Bus Specification, Feb. 1986 and Revised June 5, 1996, Philips Semiconductor (now NXP) (www.nxp.com). - Page 16 Embedian, Inc. SPI Bus – “Serial Peripheral Interface” ‐ de‐facto serial interface standard defined by Motorola. A good description may be found on Wikipedia (http://en.wikipedia.org/wiki/Serial_Peripheral_Interface_Bus). USB Specifications (www.usb.org). Serial ATA Revision 3.1, July 18, 2011, Gold Revision, © Serial ATA International Organization (www.sata‐io.org)

- Page 17 Embedian, Inc. 1.5.3. Embedian Documents The following documents are listed for reference. The Module schematic is not usually available outside of Embedian, without special permission. The other schematics will be available. Contact your Embedian representative for more information. The SMARC Evaluation Carrier Board Schematic is particularly useful as an example of the implementation of various interfaces on a Carrier board. SMARC Evaluation Carrier Board Schematic, PDF and OrCAD format SMARC Evaluation Carrier Board User’s Manual ...

- Page 18 Embedian, Inc. 1.5.5. NXP Development Tools IOMUX_TOOL v4.1 for ARM® i.MX8M Microprocessors 1.5.6. NXP Software Documents Linux 4.9.88_2.0.0 Android O8.1.0_1.3.0 8MQ GA Documentation 1.5.7. Embedian Software Documents Embedian Linux BSP for SMARC‐iMX8M Module Embedian Android BSP for SMARC‐iMX8M Module Embedian Linux BSP User’s Guide Embedian Android BSP User’s Guide 1.5.8. NXP Design Network SABRE Wandboard Nucleus SMARC-iMX8M Computer on Module User’s Manual v.1.0...

-

Page 19: Chapter 2 Specifications

Embedian, Inc. Specifications This Chapter provides SMARC‐iMX8M specifications. Section include: SMARC‐iMX8M General Functions SMARC‐iMX8M Debug Mechanical Specifications Electrical Specification Environment Specification SMARC-iMX8M Computer on Module User’s Manual v.1.0... - Page 20 Embedian, Inc. Chapter 2 Specifications 2.1 SMARC‐iMX8M General Functions 2.1.1. SMARC‐iMX8M Feature Set This section lists the complete feature set supported by the SMARC‐iMX8M module. SMARC Feature SMARC 2.0 SMARC‐iMX8M SMARC‐iMX8M Specification Specification Feature Support Feature Support Maximum Number Instances Possible Note1 LVDS LCD Display Support 1 Yes 1 (dual channel) Note2 DP/eDP 1 Yes HDMI Display Support 1 Yes 1 Serial Camera Support 2 Yes 2 (2‐lanes and 4‐lanes) USB Interface 6 Yes 4 (1 x USB 2.0 OTG, 1 ...

- Page 21 1. Dual channel LVDS interface: 2 x 18 bpp OR 2 x 24 bpp (up to 1,920 × 1,200 @60 fps at 24 bpp). Default configuration is single channel 24‐bit. To change this configuration, users need to send i2c command to SN65DSI84 MIPI_DSI to LVDS bridge. Please refer to Embedian u‐boot official BSP release. 2. DP interface is not validated! Awaits NXP formal release.

- Page 22 Embedian, Inc. 2.1.3. CPU The SMARC‐iMX8M implements NXP’s i.MX8M ARM processor. NXP CPU i.MX8M Dual i.MX8M Quad Lite i.MX8M Quad Not 1 ARM Cores 2x 1.5GHz Cortex‐A53 4x 1.5GHz Cortex‐A53 4x 1.5GHz Cortex‐A53 ARM Cores 1x Cortex‐M4F 1x Cortex‐M4F 1x Cortex‐M4F Memory Speed LPDDR4‐3200 LPDDR4‐3200 LPDDR4‐3200 L2 Cache 1MB L2 1MB L2 1MB L2 GPU GC7000Lite GC7000Lite GC7000Lite 4 shaders 4 shaders 4 shaders OpenGL ES 3.1, OpenGL ES 3.1, OpenGL ES 3.1, OpenCL 1.2, OpenGL OpenCL 1.2, OpenGL OpenCL 1.2, OpenGL 3.0, OpenVG and 3.0, OpenVG and ...

- Page 23 Embedian, Inc. 2.1.4. Onboard Storage The SMARC‐iMX8M module supports an 8GB eMMC flash memory device, and a 32Kb I2C serial EEPROM on the Module I2C_GP (I2C3) bus. The device used is an On Semiconductor 24C32 equivalent. The Module serial EEPROM is intended to retain Module parameter information, including a module serial number. The Module serial EEPROM data structure conforms to the PICMG® EEEP Embedded EEPROM Specification.). The onboard 8GB eMMC flash is used as boot media. The module will always boot up from the ...

- Page 24 Embedian, Inc. 2.1.6 LVDS Interface The SMARC‐iMX8M implements two 18 / 24 bit single channel LVDS output streams that are defined in SMARC 2.0 edge connector for the Primary displays from i.MX8M MIPI_DSI interface. They can also be configured as an 18 / 24 bit dual‐channel LVDS directly out of the SMARC Module. The LVDS LCD signals found on the SMARC‐i.MX8M offers two LVDS channels, with resolutions up to 1,920 × 1,200 @60 fps at 24 bpp. They are generated from MIPI_DSI signals from the NXP® i.MX8M Cortex A53 processor passing through a TI SN65DSI84 MIPI® DSI Bridge To FLATLINK™ LVDS. Each channel consists of one clock pair and four data pairs. The LVDS signals support the flow of MIPI DSI data from the i.MX8M CPU to external display devices through LVDS interface. The LVDS ports support the following configurations: One single channel output ...

- Page 25 Embedian, Inc. The following figure shows the LVDS LCD block diagram. Figure 2: SMARC‐iMX8M LVDS LCD Diagram SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 26 Embedian, Inc. 2.1.6.1 LVDS channel select SMARC‐iMX8 LVDS LCD interface can be configured as an 18‐bit/24‐bit single‐channel LVDS output or a dual‐channel LVDS output by accessing TI SN65DSI84 0x18 register via I2C_GP bus. The default configuration from software is 24‐bit single‐channel LVDS. User can refer to Embedian official u‐boot release and SN65DSI84 datasheet to figure out how to change to different configuration. SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 27 Embedian, Inc. 2.1.6.2 LVDS Signals Data Flow i.MX8M processor and TI SN65DSI84 implementation is shown in the following table: NXP i.MX8M CPU TI SN65DSI84 Net Names Note Ball Mode Pin Name Pin# Pin Name C16 ALT0 MIPI_DSI_CLK_N__ J5 DACN MIPI_DSI_CLK‐ MIPI_DSI_CLK_N D16 ALT0 MIPI_DSI_CLK_P__ H5 DACP MIPI_DSI_CLK+ MIPI_DSI_CLK_P A17 ALT0 ...

- Page 28 Embedian, Inc. The path from TI SN65DSI84 to the golden finger edge connector is show in the following table. TI Golden Finger Edge Net Names Note SN65DSI84 Connector Pin Pin Name Pin# Pin Name SN65DSI84, ChannelA (Default) C8 A_Y0P S125 LVDS0_0+/ LVDS0_0+ eDP0_TX0+/ LVDS0 LCD data DSI0_D0+ channel differential C9 A_Y0N S126 LVDS0_0‐/ LVDS0_0‐ ...

- Page 29 Embedian, Inc. TI Golden Finger Edge Net Names Note SN65DSI84 Connector Pin Pin Name Pin# Pin Name SN65DSI84 ChannelB B6 B_CLKP S108 LVDS1_CK+/ LVDS1_CK+ eDP1_AUX+/ LVDS1 LCD DSI1_CLK+ differential clock A6 B_CLKN S109 LVDS1_CK‐/ LVDS1_CK‐ pairs eDP1_AUX‐/ DSI1_CLK‐ B3 B_Y0P S111 LVDS1_0+/ LVDS1_0+ eDP1_TX0+/ LVDS1 LCD data DSI1_D0+ channel differential A3 ...

- Page 30 Embedian, Inc. A 24 bit dual channel LVDS implementation comprises 10 differential pairs: 4 pairs for odd pixel and control data; 1 pair for the LVDS clock for the odd data; 4 pairs for the even pixel data and control data, and 1 pair for the even LVDS clock. To use the dual channel LVDS mode, you need a display supporting the dual channel LVDS mode in order to receive odd and even pixel data. 2.1.6.3 Other LCD Control Signals The signals in the table below support the LVDS LCD interfaces (as these are created from the same i.MX8M source). Edge Golden Direction Type Description Finder Tolerance Signal Name LCD0_VDD_EN Output CMOS High enables panel VDD 1.8V LCD0_BKLT_EN Output CMOS High enables panel backlight 1.8V LCD0_BKLT_PWM Output CMOS Display backlight PWM control 1.8V I2C_LCD_DAT Bi‐Dir CMOS I2C data – to read LCD display EDID EEPROMs OD 1.8V I2C_LCD_CK ...

- Page 31 Embedian, Inc. Below list LCD control signals that mapping to CPU iomux and SMARC edge connector. NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Note Golden Finger Ball Mode Pin Name Pin# Pin Name L1 ALT5 SAI1_RXFS__ S127 LCD0_BKLT_EN LCD_ High enables GPIO4_IO0 BKLT_EN panel backlight K1 ALT5 SAI1_RXC__ S133 LCD0_VDD_EN ...

- Page 32 Embedian, Inc. support. The following figure shows the HDMI block diagram. Figure 3: SMARC‐iMX8M HDMI Diagram SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 33 Embedian, Inc. NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Note Golden Finger Ball Mode Pin Name Pin# Pin Name HDMI T2 N/A HDMI_TX_M_ P99 HDMI_D0‐/ HDMI_D0‐ TMDS / HDMI LN_0 DP1_LANE2‐ data differential pair 0 T1 N/A HDMI_TX_P_ P98 HDMI_D0+/ HDMI_D0+ LN_0 DP1_LANE2+ U1 N/A HDMI_TX_M_ P96 HDMI_D1‐/ HDMI_D1‐ TMDS / HDMI LN_1 ...

- Page 34 Embedian, Inc. 2.1.7.1 HDMI Signals The table below shows the HDMI related signals. Edge Golden Direction Type Description Finder Tolerance Signal Name HDMI_D[0:2]+ Output TDMS TMDS / HDMI data differential pairs HDMI_D[0:2]‐ HDMI_CK+ Output TDMS HDMI differential clock output pair HDMI_CK‐ HDMI_HPD Input CMOS HDMI Hot Plug Detect input 1.8V HDMI_CTRL_DAT Bi‐Dir CMOS I2C data line dedicated to HDMI OD 1.8V HDMI_CTRL_CK Bi‐Dir CMOS I2C clock line dedicated to HDMI OD 1.8V HDMI displays uses 5V I2C signaling. The Module HDMI_CTRL_DAT and HDMI_CTRL_CK signals are level translated on the Carrier from the Module ...

- Page 35 Embedian, Inc. 2.1.7.2 DP++ Operation Over SMARC HDMI Pins The SMARC‐iMX8M HDMI pins could alternatively be used for DisplayPort++ (DP++) operation. Dual Mode (HDMI and DisplayPort on the same pins) implementations could be realized. This is desirable for SOCs that natively implement this capability. The HDMI_CTRL_DAT and HDMI_CTRL_CK lines are DC coupled, but the DP_AUX+ /‐ pair must be AC coupled. A set of FET switches is used on SMARC‐iMX8M to sort this out. The FET gates are ...

- Page 36 Embedian, Inc. 2.1.7.3 Display Port Signals The table below shows the Display Port related signals. Edge Golden Direction Coupling Description Finder Tolerance Signal Name DP1_LANE[0:3]+ Output AC Coupled DP Data Pair [0:3] positive off module DP1_LANE[0:3]‐ Output AC Coupled DP Data Pair [0:3] negative off module DP1_HPD Input DC coupled DP Hot Plug Detect input CMOS 1.8V DP1_AUX‐ Bi‐Dir AC Coupled DP AUX Channel (‐ part of pair) on module DP1_AUX+ Bi‐Dir AC Coupled DP AUX Channel (+ part of pair) on module DP1_AUX_SEL Input DC coupled Pulled to GND on Carrier for DP operation in ...

- Page 37 Embedian, Inc. 2.1.8 USB Interface The Embedian SMARC‐iMX8M module supports two USB 2.0 ports (USB 0:1) and two USB 3.0 ports (USB 2:3). The USB 2.0 and USB 3.0 IP in i.MX8M processor are independent. Per the SMARC specification, the module supports a USB “On‐The‐Go” (OTG) port capable of functioning either as a ...

- Page 38 Embedian, Inc. USB interface signals are exposed on the SMARC‐iMX8M edge connector as shown below: NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Note Golden Finger Ball Mode Pin Name Pin# Pin Name USB0 Port (USB 2.0 OTG) A14 USB1_DP P60 USB0+ USB0+ USB0 data pair B14 USB1_DN P61 USB0‐ USB0‐ L20 ALT5 NAND_DATA04__ P62 USB0_EN_OC# USB0_EN_OC# USB0 power GPIO3_IO10 enable/over current indication signal D14 Turn on ...

- Page 39 Embedian, Inc. NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Note Golden Finger Ball Mode Pin Name Pin# Pin Name USB2 Port (USB 3.0 Host) A13 USB1_TX_P S71 USB2_SSTX+ USB2_SSTX+ USB2 transmit signal differential pair positive B13 USB1_TX_N S72 USB2_SSTX‐ USB2_SSTX‐ USB2 transmit signal differential pair negative A12 USB1_TX_P S74 USB2_SSRX+ USB2_SSRX+ USB2 receive signal differential pair positive ...

- Page 40 Embedian, Inc. NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Note Golden Finger Ball Mode Pin Name Pin# Pin Name USB3 Port (USB3.0 OTG) A13 USB1_TX_P S62 USB3_SSTX+ USB3_SSTX+ USB3 transmit signal differential pair positive B13 USB1_TX_N S63 USB3_SSTX‐ USB3_SSTX‐ USB3 transmit signal differential pair negative A13 USB1_TX_P S65 USB3_SSRX+ USB3_SSRX+ USB3 receive signal differential pair positive ...

- Page 41 Embedian, Inc. 2.1.8.1 USB Signals The table below shows the USB0 related signals. Edge Golden Direction Type Description Finder Tolerance Signal Name USB[0:1]+ Bi‐Dir USB Differential US 2.0 Data Pair USB[0:1]‐ USB[0:3]_EN_OC# Bi‐Dir CMOS Pulled low by Module OD driver to disable USB0 power. OD 3.3V Pulled low by Carrier OD driver to indicate over‐current situation. A 10k pull‐up is present on the Module to a 3.3V rail. The pull‐up rail may be switched off to conserve power if the USB port is not in use. Further details may be found in Section 2.1.8.2 USBx_EN_OC# Discussion below. USB0_VBUS_DET Input USB VBUS 5V USB host power detection, when this port is used as a device. USB3_VBUS_DET USB0_OTG_ID Input CMOS USB OTG ID input, active high. ...

- Page 42 Embedian, Inc. 2.1.8.2 USB[0:3]_EN_OC# Discussion The Module USB[0:3]_EN_OC# pins are multi‐function Module pins, with a 10k pull‐up to a 3.3V rail on the Module, an OD driver on the Module, and, if the OC# (over‐current) monitoring function is implemented on the Carrier, an OD driver on the Carrier. The use is as follows: 1) On the Carrier board, for external plug‐in USB peripherals (USB memory sticks, cameras, keyboards, mice, etc.) USB power distribution is typically handled by USB power switches such as the Texas Instruments TPS2052B or the Micrel MIC2026‐1 or similar devices. The Carrier implementation is more ...

- Page 43 Embedian, Inc. USB[0:3]_EN_OC# pins may be left unused, or they may be used as USB[0:3] power enables, without making use of the over‐current detect Module input feature. The SMARC‐iMX8M Module USB power enable and over current indication logic implementation is shown in the following block diagram. There are 10k pull‐up resistors on the Module on the SMARC USB[0:3]_EN_OC# lines. Outputs driving the USBx_EN_OC# lines are open‐drain. The Carrier board USB power switch, if present, is enabled by USB[0:3]_EN_OC# after a device connection is detected on the DP/DM lines. The Enable pin on the Carrier board USB power switch must be active high and ...

- Page 44 Embedian, Inc. 2.1.9. Gigabit Ethernet Controller (10/100/1000Mbps) Interface The SMARC‐iMX8M module supports one Gigabit Ethernet (10/100/1000Mbps) interfaces. The Gigabit Ethernet controller interfaces are accomplished by using the low‐power Qualcomm Atheros AR8035 physical layer (PHY) transceiver with variable I/O voltage that is compliant with the IEEE 802.3‐2005 standards. The AR8035 supports communication ...

- Page 45 Embedian, Inc. This is diagrammed below. Figure 6: Gigabit Ethernet Connection from i.MX8M to Qualcomm Atheros AR8035 SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 46 Embedian, Inc. i.MX8M processor and Qualcomm Atheros AR8035 implementation is shown in the following table: NXP i.MX8M CPU Qualcomm Net Names Note AR8035 Ball Mode Pin Name Pin# Pin Name Gigabit LAN N19 ALT0 ENET_MDIO__ 39 MDIO ENET_MDIO Serial Management ENET1_MDIO Interface data input/output N20 ALT0 ENET_MDC__ 40 MDC ENET_MDC Serial Management ENET1_MDC ...

- Page 47 Embedian, Inc. NXP i.MX8M CPU Qualcomm Net Names Note AR8035 Ball Mode Pin Name Pin# Pin Name Gigabit LAN Indicates that valid P19 ALT0 ENET_TX_CTL__ TX_EN RGMII_TX_CT transmission data ENET1_RGMII_TX_ L is present on CTL TXD[3:0]. R20 ALT0 ENET_TD0__ TXD0 RGMII_TD0 The MAC transmits ENET1_RGMII_TD0 data to the transceiver using this signal. R21 ALT0 ENET_TD1__ ...

- Page 48 Embedian, Inc. The path from AR8035 to the golden finger edge connector is show in the following table. Qualcomm Golden Finger Edge Net Names Note AR8035 Connector Pin Pin Name Pin# Pin Name AR8035 PHY 9 TRXP0 P30 GbE_MDI0+ GBE_MDI0+ Differential Transmit/Receive Positive Channel 0 10 TRXN0 P29 GbE_MDI0‐ GBE_MDI0‐ ...

- Page 49 Embedian, Inc. Qualcomm Golden Finger Edge Net Names Note AR8035 Connector Pin Pin Name Pin# Pin Name AR8035 PHY 21 LED_ACT P25 GbE_LINK_ACT# GBE_LINK_ACT# Link / Activity Indication LED Driven low on Link (10, 100 or 1000 mbps) Blinks on Activity Could be able to sink 24mA or more Carrier LED current 24 LED_10_100 P21 GbE_LINK100# GBE_LINK100# Link Speed Indication LED for 100Mbps Could be able to sink 24mA or more Carrier LED current 22 LED_1000 ...

- Page 50 Embedian, Inc. 2.1.9.1. Gigabit LAN Signals The table below shows the Gigabit LAN related signals. Edge Golden Direction Type Description Finder Tolerance Signal Name GBE_MDI0+ Bi‐Dir GBE_MDI Bi‐directional transmit/receive pair 0 to magnetics (Media Dependent Interface) GBE_MDI0‐ GBE_MDI1+ Bi‐Dir GBE_MDI Bi‐directional transmit/receive pair 1 to magnetics (Media Dependent Interface) GBE_MDI1‐ GBE_MDI2+ Bi‐Dir GBE_MDI Bi‐directional transmit/receive pair 2 to magnetics (Media Dependent Interface) GBE_MDI2‐ GBE_MDI3+ Bi‐Dir GBE_MDI Bi‐directional transmit/receive pair 3 to magnetics (Media Dependent Interface) GBE_MDI3‐ GBE_100# Output CMOS Link Speed Indication LED for 100Mbps OD ...

- Page 51 Embedian, Inc. 2.1.9.2. Suggested Magnetics Listed below are suggested magnetics. For normal temperature (0 C ~70 C) products. Vendor P/N Package Cores Temp Configuration Halo HFJ11‐1G02E Integrated 8 C~70 C HP Auto‐MDIX RJ45 UDE RB1‐BA6BT9WA Integrated 8 ‐40 C~85 C HP Auto‐MDIX RJ45 Halo TG1G‐S002NZRL 24‐pin 8 C~70 C HP Auto‐MDIX SOIC‐W For industrial temperature (‐40 C ~85 C) products. ...

- Page 52 Embedian, Inc. 2.1.10. PCIe_A and PCIe_B Interfaces The SMARC‐iMX8M offers two PCI Express x1 lanes. The PCIe signals are routed from the NXP® i.MX8M processor to the PCI Express port A and B of the SMARC‐iMX8M edge finger. These signals support PCI Express Gen. 2.1 interfaces at 5 Gb/s and are backward compatible to Gen. 1.1 interfaces at 2.5 Gb/s. Only x1 PCI Express link configuration is possible. Diodes PI6CFGL201B clock generators are used on each PCIe port to make PCIe ...

- Page 53 Embedian, Inc. PCI Express interface signals are exposed on the SMARC‐iMX8M edge connector as shown below: NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Note Golden Finger Ball Mode Pin Name Pin# Pin Name H21 ALT5 NAND_CLE__ S146 PCIE_WAKE# PCIE_WAKE# PCIe wake up GPIO3_IO5 interrupt to host PCI Express Port A F21 ALT5 NAND_CE2_B__ P75 PCIE_A_RST# PCIE_A_RST# Reset Signal GPIO3_IO3 for external devices. K25 PCIE1_REF_PAD P83 PCIE_A_REFCK+ PCIE_A_REFCK+ ...

- Page 54 Embedian, Inc. NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Note Golden Finger Ball Mode Pin Name Pin# Pin Name PCI Express Port B H20 ALT5 NAND_CE3_B__ S76 PCIE_B_RST# PCIE_B_RST# Reset Signal GPIO3_IO4 for external devices. F25 PCIE2_REF_PAD S84 PCIE_B_REFCK+ PCIE_B_REFCK+ Differential _CLK_P PCI Express Reference F24 PCIE2_REF_PAD S85 PCIE_B_REFCK‐ PCIE_B_REFCK‐ Clock Signals _CLK_P for Lanes B ...

- Page 55 Embedian, Inc. 2.1.10.1. PCIe_Link Signals The table below shows the PCIe_Link A and B related signals. Edge Golden Direction Type Description Finder Tolerance Signal Name PCI Express Port A PCIE_A_TX+ Output HCSL PCIe Differential PCIe Link A transmit data pair 0 PCIE_A_TX‐ Series coupling caps is on the Module Caps is 0402 package 0.1uF PCIE_A_RX+ Input HCSL PCIe Differential PCIe Link A receive data pair 0 PCIE_A_RX‐ No coupling caps on Module PCIE_A_REFCK+ Output HCSL PCIe Differential PCIe Link A reference clock output PCIE_A_REFCK‐ DC coupled PCIE_A_RST# Output CMOS PCIe Port A reset output 3.3V PCI Express Port B PCIE_B_TX+ Output HCSL PCIe ...

- Page 56 Embedian, Inc. 2.1.10.2. PCIe Wake Signals The table below shows the PCIe Wake signal. Edge Golden Direction Type Description Finder Tolerance Signal Name PCIE_WAKE# Input CMOS 3.3V PCIe wake up interrupt to host – common to PCIe links A, B, C – pulled up or terminated on Module SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 57 Embedian, Inc. 2.1.11. MIPI/CMOS Serial Camera Interface (MIPI_CSI) The NXP® i.MX8M provides connectivity to cameras via the MIPI/CSI‐2 transmitter and maintains image manipulation and processing with adequate synchronization and control. The Camera Serial Interface (CSI) controls the camera port and provides interface to an image sensor or a ...

- Page 58 Embedian, Inc. The following figure shows the serial camera interface block diagram. Figure 8. MIPI/Serial Camera Interface Block Diagram SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 59 Embedian, Inc. MIPI/Serial Camera interface signals are exposed on the SMARC‐iMX8M edge connector as shown below: NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Note Golden Finger Ball Mode Pin Name Pin# Pin Name MIPI/Serial Camera Interface 1 (CSI0) K7 ALT5 GPIO1_IO14__ S6 CAM_MCK CAM_MCK Master clock PWM3_OUT output for CSI camera support A22 ALT0 MIPI_CSI1_CLK_N S9 CSI0_CK‐ CSI0_CK‐ CSI0 differential B22 ALT0 MIPI_CSI1_CLK_P S8 CSI0_CK+ CSI0_CK+ ...

- Page 60 Embedian, Inc. 2.1.11.1. Camera I2C Support The I2C_CAM0/1 port is intended to support serial and parallel cameras. Most contemporary cameras with I2C support allow a choice of two I2C address ranges. NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Note Golden Finger Ball Mode Pin Name Pin# Pin Name I2C_CAM0 G7 ALT0 I2C2_SCL__ S5 CSI0_TX+/ I2C_CAM0_CK I2C2_SCL I2C_CAM0_CK F7 ALT0 I2C2_SDA__ S7 ...

- Page 61 Embedian, Inc. Edge Golden Direction Type Description Finder Tolerance Signal Name I2C_CAM0 I2C_CAM0_DAT Bi‐Dir CMOS Serial camera support link ‐ I2C data OD 1.8V I2C_CAM0_CK Bi‐Dir CMOS Serial camera support link ‐ I2C clock OD 1.8V I2C_CAM1 I2C_CAM1_DAT Bi‐Dir CMOS Serial camera support link ‐ I2C data OD 1.8V I2C_CAM1_CK Bi‐Dir CMOS Serial camera support link ‐ I2C clock OD 1.8V 2.1.11.2. MIPI Serial Camera In – MIPI CSI0/1 Edge Golden ...

- Page 62 Embedian, Inc. 2.1.12 SD/SDMMC Interface SMARC‐iMX8M is configured to support two MMC controllers. One is used for on‐module 8‐bit eMMC support, and the other one is used for external SDHC/SDIO interface. The SMARC‐iMX8M module supports one 4‐bit SDIO interface, per the SMARC 2.0 specification. The SDIO interface uses 3.3V signaling, per the SMARC spec and for compatibility with commonly available SDIO cards. The following figure shows the SDIO block diagram. Figure 9. SD/SDIO/eMMC Interface Block Diagram SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 63 Embedian, Inc. SDIO interface signals are exposed on the SMARC golden finger edge connector as shown below: NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Note Golden Finger Ball Mode Pin Name Pin# Pin Name SD/SDIO N22 ALT0 SD2_DATA0__ P39 SDIO_D0 SDIO_D0 SDIO Data 0 SD2_USDHC2_ DATA0 N21 ALT0 SD2_DATA1__ P40 SDIO_D1 ...

- Page 64 Embedian, Inc. schematic is useful as an implementation reference. 2. If SD boot up function is required, the pull‐up resistor to 3.3V of SDIO_PWR_EN # should be 4.7k or less. 3. SDIO_WP and SDIO_CD# are 10k pull up to 3.3V on module. 2.1.12.1. SDIO Card (4 bit) Interface The Carrier SDIO Card can be selected as the Boot Device (See section 4.3). Edge Golden Direction Type Description Finder ...

- Page 65 Embedian, Inc. 2.1.13 SPI/eSPI Interface The SMARC‐iMX8M module supports two NXP i.MX8M SPI interfaces that are available off‐Module for general purpose use. One of them is implemented as eSPI interface by SMARC 2.0 definition. Each SPI channel has two chip‐selects that can connect two SPI slave devices on each channel. SPI devices will share the "SPI0_DIN", "SPI0_DO" and "SPI0_CK" pins, but ...

- Page 66 Embedian, Inc. The SPI interface is diagramed below. Figure 10: SPI Interface Block Diagram SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 67 Embedian, Inc. SPI interface signals are exposed on the SMARC golden finger edge connector as shown below: NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Note Golden Finger Ball Mode Pin Name Pin# Pin Name SPI0 Port D4 ALT5 ECSPI1_SS0__ P43 SPI0_CS0# SPI0_CS0# SPI0 Master Chip GPIO5_IO9 Select 0 output T6 ALT5 GPIO1_IO00__ P31 SPI0_CS1# SPI0_CS1# SPI0 Master Chip GPIO1_IO0 Select 1 output D5 ALT0 ECSPI1_SCLK__ P44 SPI0_CK SPI0_SCLK ...

- Page 68 Embedian, Inc. NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Note Golden Finger Ball Mode Pin Name Pin# Pin Name eSPI Port NAND_CE0_B__ H19 ALT1 P54 ESPI_CS0# ESPI_CS0# QSPI Master Chip QSPI_A_SS0_B Select 0 output G21 ALT1 NAND_CE1_B__ P55 ESPI_CS1# ESPI_CS1# QSPI Master Chip QSPI_A_SS1_B Select 1 output G19 ALT1 NAND_ALE__ P56 ESPI_CK ESPI_SCLK QSPI Master Clock QSPI_A_SCLK output ...

- Page 69 Embedian, Inc. 2.1.13.1. SPI0 Signals i.MX8M processor ROM does not support SPI0 device boot up. The Carrier SPI0 device cannot be selected as the Boot Device – see Section 4.3 Boot Select. Edge Golden Direction Type Description Finder Tolerance Signal Name SPI0_CS0# Output CMOS SPI0 Master Chip Select 0 output 1.8V SPI0_CS1# Output CMOS SPI0 Master Chip Select 1 output 1.8V SPI0_CK Output CMOS SPI0 Master Clock output 1.8V SPI0_DIN Input CMOS SPI0 Master Data input (input to CPU, output 1.8V from SPI device) SPI0_DO Output CMOS SPI0 Master Data output (output from CPU, 1.8V input to SPI device) ...

- Page 70 Embedian, Inc. 2.1.13.2. ESPI Signals i.MX8M processor ROM does not support QSPI device boot up either. The Carrier QSPI device cannot be selected as the Boot Device – see Section 4.3 Boot Select. Edge Golden Direction Type Description Finder Tolerance Signal Name ESPI_CS0# Output CMOS QSPI Master Chip Select 0 output 1.8V ESPI_CS1# Output CMOS QSPI Master Chip Select 1 output 1.8V ESPI_CK Output CMOS QSPI Master Clock output 1.8V ESPI_IO_[0:3] Bi‐Dir CMOS QSPI Master Data input/output 1.8V ESPI_RESET# Output CMOS QSPI Reset Reset the QSPI interface for both 1.8V master and slaves. ESPI_ALERT[0:1]# ...

- Page 71 Embedian, Inc. 2.1.14. I2S Interface The SMARC‐iMX8M module uses I2S format for Audio signals. These signals are derived from the Synchronous Audio Interface (SAI) of the NXP® i.MX8M processor. The Serial Audio Interface (SAI) implements a synchronous serial bus interface for connecting digital audio devices. It is by far the most common mechanism used to transfer two channels of audio data between devices within a system. SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 72 Embedian, Inc. SMARC‐iMX8M supports two I2S instances (I2S0 and I2S2). I2S interface signals are exposed on the SMARC‐iMX8M golden finger edge connector as shown below: NXP i.MX8M CPU SMARC‐iMX8M Net Names Note Edge Golden Finger Ball Mode Pin Name Pin Name # H5 ALT0 SAI2_MCLK__ AUDIO_MCK AUD_MCLK Master clock SAI2_MCLK output to Audio codecs I2S0 interface H4 ALT0 SAI2_TXFS__ I2S0_LRCK ...

- Page 73 Embedian, Inc. Note: SGTL5000 I2S audio codec is used in EVK‐STD‐CARRIER‐S20 evaluation carrier board. 2.1.14.1 I2S Signals Edge Golden Direction Type Description Finder Tolerance Signal Name AUDIO_MCK Output CMOS Master clock output to Audio codecs 1.8V I2S0 Signals I2S0_LRCK Bi‐Dir CMOS Left& Right audio synchronization clock 1.8V I2S0_SDOUT Output CMOS Digital audio Output 1.8V I2S0_SDIN Input ...

- Page 74 Embedian, Inc. 2.1.15. Asynchronous Serial Port (UARTs) The SMARC‐iMX8M module supports four UARTs (SER0:3). UART SER0 and SER2 support flow control signals (RTS#, CTS#). UART SER1 and SER3 do not support flow control (TX, RX only). When working with software, SER3 is used for SMARC‐iMX8M debugging console port. The module asynchronous serial port signals have a VDDIO (1.8V) level ...

- Page 75 Embedian, Inc. Asynchronous serial ports interface signals are exposed on the SMARC golden finger edge connector as shown below: NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Note Golden Finger Ball Mode Pin Name Pin# Pin Name SER0 Port D7 ALT0 UART4_TXD__ P129 SER0_TX SER0_TX Asynchronous serial port data out UART4_DCE_TX C6 ALT0 UART4_RXD__ P130 SER0_RX SER0_RX ...

- Page 76 Embedian, Inc. NXP i.MX8M CPU SMARC‐iMX8M Net Names Note Edge Golden Finger Ball Mode Pin Name Pin# Pin Name SER2 Port D6 ALT0 UART2_TXD__ P136 SER2_TX SER2_TX Asynchronous serial port data UART2_DCE_TX out B6 ALT0 UART2_RXD__ P137 SER2_RX SER2_RX Asynchronous serial port data in UART2_DCE_RX E5 ALT5 ECSPI2_MOSI__ P138 SER2_RTS# SER2_RTS# Request to Send ...

- Page 77 Embedian, Inc. 2.1.15.1. UART Signals Module pins for up to four asynchronous serial ports are defined. The ports are designated SER0 – SER3. Ports SER0 and SER2 are 4 wire ports (2 data lines and 2 handshake lines). Ports SER1 and SER3 are 2 wire ports (data only). Edge Golden Direction Type Description Finder Tolerance Signal Name SER[0:3]_TX Output CMOS Asynchronous serial port data out 1.8V SER[0:3]_RX Input CMOS Asynchronous serial port data in 1.8V SER[0]_RTS# Output CMOS Request to Send handshake line for SER0 1.8V SER[0]_CTS# Input CMOS Clear to Send handshake line for SER0 1.8V SER[2]_RTS# Output CMOS Request to Send handshake line for SER2 1.8V SER[2]_CTS# ...

- Page 78 Embedian, Inc. 2.1.16. I2C Interface There is a minimum configuration of I2C ports up to a maximum of 6 ports defined in the SMARC specification: PM (Power Management), LCD (Liquid Crystal Display), GP (General Purpose), CAM0 (Camera 0), CAM1 (Camera 1) and HDMI. SMARC‐iMX8M does not have HDMI interface, it defines five out of the six I2C buses and supports multiple masters and slaves in fast mode (400 KHz operation). All I2C interfaces are implemented directly from NXP i.MX8M processor interfaces. Figure 11. I2C Interface Block Diagram SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 79 Embedian, Inc. This will be summarized below. I2C Port Primary Purpose Alternative Use I/O Voltage Level Golden i.MX8M Finger CPU Connector Power System CMOS Management configuration I2C_PM I2C1 1.8V support management I2C_GP I2C3 General purpose CMOS use 1.8V LCD display CMOS support, to read I2C_LCD I2C2 General Purpose 1.8V LCD display EDID EEPROMs (for parallel and LVDS LCD,) I2C_CAM0 I2C2 ...

- Page 80 Embedian, Inc. The I2C interface signals are exposed on the SMARC golden finger edge connector as shown below: NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Note Golden Finger Ball Mode Pin Name Pin# Pin Name I2C_PM E7 ALT0 I2C1_SCL__ P121 I2C_PM_CK I2C_PM_CK Power I2C1_SCL management I2C bus clock E8 ALT0 I2C1_SDA__ P122 I2C_PM_DAT ...

- Page 81 Embedian, Inc. NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Note Golden Finger Ball Mode Pin Name Pin# Pin Name 2C_HDMI F8 N/A I2C4_SCL__ P105 HDMI_CTRL_ HDMI_CTRL_ HDMI I2C bus clock I2C4_SCL CK CK F8 N/A I2C4_SDA__ P106 HDMI_CTRL_ HDMI_CTRL_ HDMI I2C bus data I2C4_SDA DAT DAT SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 82 Embedian, Inc. Note: All I2C bus and are operated at 1.8V. The slave devices and their address details are listed in the following table: Address # Device Description Address (8‐bit) Notes (7‐bit) Read Write I2C_PM (I2C1) Bus Pericom PCIe Gen 1‐2‐3 0x68 0xD1 0xD0 Clock Generator for Clock Generator PI6CFGL201BZDIE PCIe Lane A Pericom PCIe Gen 1‐2‐3 ...

- Page 83 Embedian, Inc. 2.1.17. CAN Bus Interface The Controller Area Network (CAN) is a serial communications protocol which efficiently supports distributed real‐time control with a high level of security. The SMARC‐iMX8M module implements two CAN bus interfaces from Microchip MCP2515 SPI to CAN interface IC. The SPI bus used to interface with MCP2515 CAN controller is SPI0. The chip select SS2# is reserved for CAN0 and SS3# is reserved for CAN1. Chip selects SS0# and SS1# are connected to MXM golden finger connector for users to use. The logic level for CAN0/1 TX/RX is 1.8V as defined in SMARC 2.0. SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 84 Embedian, Inc. The following figure shows the CAN bus block diagram. Figure 12: SMARC‐iMX8M CAN Bus Diagram SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 85 Embedian, Inc. 2.1.17.1 CAN0 Bus Signals Data Flow i.MX8M processor and Micochip MXP2515T implementation for CAN0 is shown in the following table: NXP i.MX8M CPU Microchip MCP2515T Net Names Note Ball Mode Pin Name Pin# Pin Name B4 ALT0 ECSPI1_MISO__ 15 SO SPI_CAN_SO ECSPI1_MISO A4 ALT0 ECSPI1_MOSI__ 14 SI SPI_CAN_SI ECSPI1_MOSI D5 ALT0 ECSPI1_SCLK__ 12 ...

- Page 86 Embedian, Inc. 2.1.17.2 CAN1 Bus Signals Data Flow i.MX8M processor and Micochip MXP2515T implementation for CAN1 is shown in the following table: NXP i.MX8M CPU Microchip MCP2515T Net Names Note Ball Mode Pin Name Pin# Pin Name B4 ALT0 ECSPI1_MISO__ 15 SO SPI_CAN_SO ECSPI1_MISO A4 ALT0 ECSPI1_MOSI__ 14 SI SPI_CAN_SI ECSPI1_MOSI D5 ALT0 ECSPI1_SCLK__ 12 ...

- Page 87 Embedian, Inc. 2.1.17.3 SPI to CAN Bridge Signals Data Flow The path from Mrcrochip MCP2515T to the golden finger edge connector is show in the following table. Microchip Golden Finger Edge Net Names Note MCP2515T Connector Pin Pin Name Pin# Pin Name CAN0 Bus 19 TXCAN P143 CAN0_TX CAN0_TX CAN0 Transmit output 20 RXCAN P144 CAN0_RX CAN0_RX CAN0 Receive input CAN1 Bus 19 ...

- Page 88 Embedian, Inc. 2.1.17.4. CAN0 BUS Signals Edge Golden Direction Type Description Finder Tolerance Signal Name CAN0_TX Output CMOS CAN0 Transmit output 1.8V CAN0_RX Input CMOS CAN0 Receive input 1.8V 2.1.17.5. CAN1 BUS Signals Edge Golden Direction Type Description Finder Tolerance Signal Name CAN1_TX Output CMOS CAN1 Transmit output 1.8V CAN1_RX ...

- Page 89 Embedian, Inc. 2.1.18. GPIOs The SMARC‐iMX8M module supports 12 GPIOs, as defined by the SMARC specification. Specific alternate functions are assigned to some GPIOs such as PWM / Tachometer capability, Camera support, CAN Error Signaling and HD Audio reset. All pins are capable of bi‐directional operation. A default direction of operation is assigned, with half of them (GPIO0 – GPIO5) for use as outputs and the remainder (GPIO6 – GPIO11) as inputs by SMARC ...

- Page 90 Embedian, Inc. GPIO signals are exposed on the SMARC golden finger edge connector as shown below: NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Note Golden Finger Ball Mode Pin Name Pin# Pin Name GPIOs K4 ALT5 SAI5_MCLK__ P108 GPIO0/CAM0_PWR# GPIO0 Camera 0 Power Enable, active GPIO3_IO25 low output N4 ALT5 SAI5_RXFS__ P109 GPIO1/CAM1_PWR# GPIO1 ...

- Page 91 Embedian, Inc. 2.1.18.1. GPIO Signals Twelve Module pins are allocated for GPIO (general purpose input / output) use. All pins are capable of bi‐directional operation. By SMARC specification, GPIO0 – GPIO5 are recommended for use as outputs and the remainder (GPIO6 – GPIO11) as inputs. At Module power‐up, the state of the GPIO pins may not be defined, and may briefly be configured in the “wrong” state, before boot loader code corrects them. Carrier designers should be aware of this and plan accordingly. All GPIO pins are capable of generating interrupts. The interrupt characteristics (edge or level sensitivity, polarity) are generally configurable in the i.MX8M register set. Edge Golden Finder Preferre Type Description Signal Name d Tolerance Directio n GPIO0/CAM0_PWR# Output CMOS Camera 0 Power Enable, active low output 1.8V GPIO1/CAM1_PWR# Output CMOS Camera 1 Power Enable, active low output 1.8V GPIO2/CAM0_RST# Output CMOS Camera 0 Reset, active low output 1.8V GPIO3/CAM1_RST# Output CMOS ...

- Page 92 Embedian, Inc. 2.1.19 Watchdog Timer Interface i.MX8M features an internal WDT. Embedian’s Linux kernel enables the internal i.MX8M WDT and makes this functionality available to users through the standard Linux Watchdog API. A description of the API is available following the link below: http://www.kernel.org/doc/Documentation/watchdog/watchdog‐api.txt WDT signals are exposed on the SMARC golden finger edge connector as shown below: NXP i.MX8M CPU ...

- Page 93 Embedian, Inc. 2.1.20 JTAG Figure 13 shows the SMARC‐iMX8M JTAG connectors location and pin out. Figure 13: JTAG Connector Location and Pinout JTAG functions for CPU debug and test are implemented on separate small form factor connector (CN3: JST SM10B‐SRSS‐TB, 1mm pitch R/A SMD Header). The JTAG pins are used to allow test equipment and circuit emulators to have access to the Module CPU. The pin‐outs shown below are used: SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 94 Embedian, Inc. NXP i.MX8M CPU JTAG(Connector: JST Type Note SM10B‐SRSS‐TB, 1mm pitch R/A SMD Header) Ball Mode Pin Name Pin# Pin Name JTAG 1 VDD_33A Power JTAG I/O Voltage (sourced by Module) U6 ATL0 JTAG_TRST_B 2 nTRST I JTAG Reset, active low V5 ALT0 JTAG_TMS 3 TMS I JTAG mode select U5 ALT0 JTAG_TDO 4 ...

- Page 95 Embedian, Inc. 2.1.21 Boot ID EEPROM The SMARC‐iMX8M module includes an I2C serial EEPROM available on the I2C_GP bus. An On Semiconductor 24C32 or equivalent EEPROM is used in the module. The device operates at 1.8V. The Module serial EEPROM is placed at I2C slave addresses A2 A1 A0 set to 0 (I2C slave address 50 hex, 7 bit address format or A0 / A1 hex, 8 bit format) (for I2C EEPROMs, address bits A6 A5 A4 A3 are set to binary 0101 convention). The module serial EEPROM is intended to retain module parameter information, including serial number. The module serial EEPROM data structure conforms to the PICMG® EEEP Embedded EEPROM Specification. ...

- Page 96 Embedian, Inc. Name Size (Bytes) Contents Header 4 MSB 0xEE3355AA LSB Board Name 8 Name for Board in ASCII “SMC8MQ2G” = Embedian SMARC‐iMX8M Computer on Module with Dual/Quad Core and 2GB LPDDR4 Configuration “SMC8MQ4G” = Embedian SMARC‐iMX8M Computer on Module with Dual/Quad Core and 4GB LPDDR4 Configuration “SMC8ML2G” = Embedian SMARC‐iMX8M Computer on Module with Quad Lite Core and 2GB LPDDR4 Configuration “SMC8ML4G” = Embedian SMARC‐iMX8M Computer on Module with Quad Lite Core and 4GB LPDDR4 Configuration Version 4 Hardware version code for version in ASCII “00A0” = rev. A0 Serial Number 12 Serial number of the board. This is a 12 character string which is: WWYYMSD1nnnn Where: WW = 2 digit week of the year of production YY = 2 digit year of production MS = Module Serial Number D1/Q1/D2/Q2/UC/SC = CPU Core and DDR Configuration Variants nnnn = incrementing board number Configuration 32 Codes to show the configuration setup on this ...

-

Page 97: Mechanical Specifications

Embedian, Inc. 2.2 SMARC‐iMX8M Debug 2.2.1. Serial Port Debug SMARC module has 4 serial output ports, SER0, SER1, SER2 and SER3. Out of these 4 serial ports, SER3 is set as the serial debug port use for i.MX8M from Embedian. Users can change to any port they want to from u‐boot defconfig file. SER3 is exposed (along with all other serial ports available on the module) in the SMARC‐iMX8M Evaluation Carrier. The default baud rate setting is 115,200 8N1. SER3 pin out of the SMARC‐iMX8M is shown below: NXP i.MX8M CPU SMARC‐iMX8M Edge Net Names Notes Golden Finger mode Pin Name Pin# ... - Page 98 Embedian, Inc. 2.3.3. Height on Bottom 0.9mm maximum (without PCB) complied with SMARC specification defines as 1.3mm as the maximum. 2.3.4. Mechanical Drawings The mechanical information is shown in Figure 14: SMARC‐iMX8M Mechanical Drawings (Top View) and Figure 15: SMARC‐iMX8M Mechanical Drawings (Bottom View)) Figure 14. SMARC‐iMX8M Mechanical Drawings (Top View) SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 99 Embedian, Inc. Figure 15. SMARC‐iMX8M Mechanical Drawings (Bottom View) The figure on the following page details the 82mm x 50mm Module mechanical attributes, including the pin numbering and edge finger pattern. SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 100 Embedian, Inc. Figure 16: SMARC-iMX8M Module Mechanical Outline SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 101 Embedian, Inc. Top side major component (IC and Connector) information is shown in Figure 17: SMARC‐iMX8M Top side components. Figure 17. SMARC‐iMX8M Top Side Components SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 102 Embedian, Inc. Bottom side major component (IC and Connector) information is shown in Figure 18: SMARC‐iMX8M Bottom side components. Figure 18. SMARC‐iMX8M Bottom Side Components SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 103 Embedian, Inc. SMARC‐iMX8M height information from Carrier board Top side to tallest Module component is shown in Figure 19: SMARC‐iMX8M Minimum “Z” Height: TOP Side 5.7mm Component 3mm Carrier Connector Module PCB 1.2mm BOT Side 1.5mm Component 1.3mm Carrier PCB 1.6mm Figure 19. SMARC‐iMX8M Minimum “Z” Height ...

- Page 104 Embedian, Inc. 2.3.5. Carrier Board Connector PCB Footprint Figure 20: Carrier Board Connector PCB Footprint Note: The hole diameter for the 4 holes (82mm x 50mm Module) or 7 holes (82mm x 80mm Module) depends on the spacer hardware selection. See the section below for more information on this. SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 105 Embedian, Inc. 2.3.6. Module Assembly Hardware The SMARC‐iMX8M module is attached to the carrier with four M2.5 screws. A 4mm length screw is usually used. The attachment holes are located on the corners of the module. Attachment holes have a 6mm diameter pad, 2.7 mm dia drill hole as shown Figure 14: SMARC‐iMX8M Mechanical Drawings (Top View) 2.3.7. Carrier Board Standoffs Figure 21: Screw Fixation Standoffs secured to the Carrier board are expected. The standoffs are to be used with M2.5 hardware. Most implementations will use Carrier board standoffs that have M2.5 threads (as opposed to clearance holes). A short ...

- Page 106 Embedian, Inc. spacer for the 5mm stack would likely be a standard length. Penn Engineering and Manufacturing (PEM) (www.pemnet.com) makes surface mount spacers with M2.5 internal threads. The product line is called SMTSO (“surface mount technology stand offs”). The shortest standard length offered is 2mm. A custom part with 1.5mm standoff length, M2.5 internal thread, and 5.56mm standoff OD is available from PEM. The Carrier PCB requires a 4.22mm hole and 6.2mm pad to accept these parts. Other vendors such as RAF Electronic Hardware (www.rafhdwe.com) offer ...

- Page 107 Embedian, Inc. The Carrier board connector is a 314 pin 0.5mm pitch right angle part designed for use with 1.2mm thick mating PCBs with the appropriate edge finger pattern. The connector is commonly used for MXM3 graphics cards. The SMARC Module uses the connector in a way quite different from the ...

- Page 108 Embedian, Inc. Vender Vendor P/N Stack Body Contact Pin Body Color Height Height Plating Style Foxconn AS0B821‐S55B ‐ *H 2.7mm 5.5mm Flash Std Black Foxconn AS0B821‐S55N ‐ *H 2.7mm 5.5mm Flash Std Ivory Foxconn AS0B826‐S55B ‐ *H 2.7mm 5.5mm 10 u‐in Std Black Foxconn AS0B826‐S55N ‐ *H 2.7mm 5.5mm 10 u‐in Std ...

- Page 109 Embedian, Inc. Note: 1. Yamaichi CN113‐314‐2001 is automotive grade. 2. The vendor drawings for the connectors listed above show a PCB footprint pattern for use with an MXM3 graphics card. This footprint, and the associated pin numbering, is not suitable for SMARC use. The MXM3 standard gangs large groups of pins together to provide ~80W capable power paths needed for X86 graphics cards. The SMARC module “ungangs” these pins to allow more signal pins. Footprint and pin numbering information for application of this 314 pin connector to SMARC is given in the sections below. 2.3.9. Module Cooling Solution—Heat Spreader A standard heat‐spreader plate for use with the SMARC 82mm x 50mm form factor is described below. A standard heat spreader plate definition allows ...

- Page 110 Embedian, Inc. Figure 23: Heat Spreader The internal square in the figure above is a thermally conductive and mechanically compliant Thermal Interface Material (or “TIM”). The exact X‐Y position and Z thickness details of the TIM vary from design to design. The two holes immediately adjacent to the TIM serve to secure the PCB in the SOC area and compress the TIM. The four interior holes that are further from the center allow a heat sink to be attached to the heat spreader plate, or they can be used to secure the heat spreader plate to a chassis wall that serves as a heat sink. Dimensions and further details may be found in the following figure. SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 111 Embedian, Inc. Dimensions in the figure above are in millimeters. “TIM” stands for “Thermal Interface Material”. The TIM takes up the small gap between the SOC top and the Module ‐ facing side of the heat spreader. SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 112 Embedian, Inc. Hole Reference Description Size A SMARC Module corner Hole size depends on standoffs used. mounting holes Spacing Standoff diameter must be compatible determined by SMARC with SMARC Module mounting hole pad specification for 82mm x and hole size (6.0mm pads, 2.7mm holes 50mm Modules. on the Module). The holes and standoffs are for use with M2.5 screw hardware. Typically these holes have 3mm length press fit or The far side of these holes are swaged clearance standoffs on counter‐sunk to allow the attachment the Module side. screw to be flush with the far side heat spreader surface. These holes are typically countersunk on the far side of the plate, to allow the heat spreader plate to be flush with a secondary heat sink. B Not Defined C Fixed location holes to allow M3 threaded holes the attachment of a heat sink to the heat spreader, or to allow the heat spreader to be ...

-

Page 113: Electrical Specifications

Embedian, Inc. 2.4 Electrical Specifications 2.4.1. Supply Voltage The SMARC‐iMX8M module operates over an input voltage range of 3.0V to 5.25V. Power is provided from the carrier through 10 power pins as defined by the SMARC specification. Caution! A single 5V DC input is recommended. 2.4.2. RTC/Backup Voltage 3.0V RTC backup power is provided through the VDD_RTC pin from the carrier board. This connection provides back up power to the module PMIC. The RTC is powered via the primary system 3.3V supply during normal operation and via the VBAT power input, if it is present, during power‐off. 2.4.3. No Separate Standby Voltage The SMARC‐iMX8M does not have a standby power rail. Standby operation is powered through the main supply voltage rail, as defined in the SMARC ... - Page 114 Embedian, Inc. 2.4.5. MTBF The SMARC‐iMX8M System MTBF (hours) : >100,000 hours The above MTBF (Mean Time Between Failure) values were calculated using a combination of manufacturer’s test data, if the data was available, and a Bellcore calculation for the remaining parts. The Bellcore calculation used is “Method 1 Case 1”. In that particular method the components are assumed to be operating at a 50 % stress level in a 40° C ambient environment and the system is assumed to have not been burned in. Manufacturer’s data has been used wherever possible. The manufacturer’s data, when used, is specified at 50 C, so in that sense the following results are slightly conservative. The MTBF values shown below are for a 40 C ...

- Page 115 Embedian, Inc. Power consumption values were recorded during the following stages: Yocto Morty • Desktop Idle • 100% CPU workload • 100% CPU workload at approximately 100°C peak power consumption Note: With the linux stress tool, we stressed the CPU to maximum frequency. The table below provides additional information about the different variants offered by the SMARC‐iMX8M. SMARC Part Number Desktop Idle 100% workload Max. power consumption (Amp/Watts) SMARC‐iMX8M‐D‐2G TBD TBD TBD SMARC‐iMX8M‐Q‐2G TBD TBD TBD SMARC‐iMX8M‐L‐2G ...

-

Page 116: Environmental Specifications

Embedian, Inc. 2.5 Environmental Specifications 2.5.1. Operating Temperature The SMARC‐iMX8M module operates from 0°C to 80°C air temperature, without a passive heat sink arrangement. Industrial temperature (‐40 C C is also available with different part number SMARC‐iMX8M‐X‐XX‐I). 2.5.2. Humidity Operating: 10% to 90% RH (non‐condensing). Non‐operating: 5% to 95% RH (non‐condensing). 2.5.3. ROHS/REACH Compliance The SMARC‐iMX8M module is compliant to the 2002/95/EC RoHS directive and REACH directive. ... -

Page 117: Chapter 3 Connector Pinout

Embedian, Inc. Connector PinOut This Chapter gives detail pinout of SMARC‐iMX8M golden finger edge connector. Section include: SMARC‐iMX8M Connector Pin Mapping SMARC-iMX8M Computer on Module User’s Manual v.1.0... - Page 118 Embedian, Inc. Chapter 3 Connector Pinout The Module pins are designated as P1 – P156 on the Module Primary (Top) side, and S1 – S158 on the Module Secondary (Bottom) side. There are total of 314 pins on the Module. The connector is sometimes identified as a 321 pin connector, but 7 pins are lost to the key (4 on the primary side and 3 on secondary side). The Secondary (Bottom) side faces the Carrier board when a normal or ...

- Page 119 Embedian, Inc. Figure 25: SMARC‐iMX8M edge finger secondary pins The next tables describe each pin, its properties, and its use on the module and development board. The “SMARC Edge Finger” column shows the connection of the signals defined in the SMARC specification. The “NXP i.MX8M CPU” column shows the connection of the CPU signals on the module. The format of this column is ...

- Page 120 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name P1 SMB_ALERT_1V8# Not used P2 GND P Ground P3 CSI1_CK+ I CSI1 differential clock B19 MIPI_CSI2_CLK_ P inputs P4 CSI1_CK‐ A19 MIPI_CSI2_CLK_ I CSI1 differential clock N inputs P5 GBE1_SDP Not used P6 GBE0_SDP Not used ...

- Page 121 Embedian, Inc. P18 GND P Ground SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name P18 GND P Ground P19 GbE0_MDI3‐ AIO Qualcomm AR8035 Differential Transmit/Receive Negative Channel 3 P20 GbE0_MDI3+ AIO Qualcomm AR8035 Differential Transmit/Receive Positive Channel 3 P21 GbE0_LINK100# O OD Link Speed Indication LED for 100Mbps Could be able to sink 24mA or more Carrier ...

- Page 122 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name P26 GbE0_MDI1‐ AIO Qualcomm AR8035 Differential Transmit/Receive Negative Channel 1 P27 GbE0_MDI1+ AIO Qualcomm AR8035 Differential Transmit/Receive Positive Channel 1 P28 GbE0_CTREF O Qualcomm AR8035 Center tap reference voltage for GBE Carrier board Ethernet magnetic P29 GbE0_MDI0‐ AIO Qualcomm AR8035 Differential Transmit/Receive ...

- Page 123 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name P31 SPI0_CS1# T6 ALT5 GPIO1_IO00__ O SPI0 Master Chip GPIO1_IO0 Select 1 output. P32 GND P Ground P33 SDIO_WP M21 ALT5 SD2_WP__ I Write Protect GPIO2_IO20 P34 SDIO_CMD M22 ALT0 SD2_CMD__ IO Command Line ...

- Page 124 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name P43 SPI0_CS0# D4 ALT5 ECSPI1_SS0__ O SPI0 Master Chip GPIO5_IO9 Select 0 output, P44 SPI0_CK D5 ALT0 ECSPI1_SCLK__ O SPI0 Master Clock ECSPI1_SCLK output P45 SPI0_DIN B4 ALT0 ECSPI1_MISO__ I SPI0 Master Data ECSPI1_MISO input (input to CPU, output from SPI ...

- Page 125 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name NAND_CE0_B__ P54 ESPI1_CS0# H19 ALT1 O SPI1 Master Chip QSPI_A_SS0_B Select 0 output P55 O SPI1 Master Chip ESPI1_CS1# G21 ALT1 NAND_CE1_B__ QSPI_A_SS1_B Select 1 output P56 ESPI1_CK G19 ALT1 NAND_ALE__ O SPI1 Master Clock QSPI_A_SCLK output P57 ESPI1_IO_1 ...

- Page 126 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name P63 USB0_VBUS_DET D14 Turn on I USB host power USB_OTG_VBUS detection, when this port is used as a device P64 USB0_OTG_ID C14 USB1_ID I USB OTG ID input, active high P65 USB1+ A10 USB_H1_DP IO Differential USB0 data pair P66 USB1‐ B10 USB_H1_DN IO ...

- Page 127 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name P71 USB2_EN_OC# L19 ALT5 NAND_DATA06__ IO Pulled low by GPIO3_IO12 OD Module OD driver to disable USB0 power Pulled low by Carrier OD driver to indicate over‐current situation If this signal is used, a pull‐up is required on the Carrier P72 RSVD Not used P73 RSVD Not used P74 USB3_EN_OC# ...

- Page 128 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name P75 PCIE_A_RST# F21 ALT5 NAND_CE2_B__ O Reset Signal for GPIO3_IO3 external devices. P76 USB4_EN_OC# Not used P77 RSVD Not used P78 RSVD Not used P79 GND P Ground P80 PCIE_C_REFCK+ Not used P81 PCIE_C_REFCK‐ Not used P82 ...

- Page 129 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name P92 HDMI_D2+ / N2 N/A HDMI_TX_P_ O TMDS / HDMI data LN_2 DP1_LANE0+ differential pair 2 / DP Data Pair 0+ P93 HDMI_D2‐ / N1 N/A HDMI_TX_M_ O TMDS / HDMI data LN_2 DP1_LANE0‐ differential pair 2/ DP Data Pair 0‐ P94 GND P Ground P95 HDMI_D1+/ U2 ...

- Page 130 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name P98 HDMI_D0+/ T1 N/A HDMI_TX_P_ O TMDS / HDMI data LN_0 DP1_LANE2+ differential pair 0 P99 HDMI_D0‐/ O TMDS / HDMI data T2 N/A HDMI_TX_M_ LN_0 DP1_LANE2‐ differential pair 0 P100 GND P Ground P101 HDMI_CK+/ M1 N/A HDMI_TX_P_ ...

- Page 131 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name K4 ALT5 SAI5_MCLK__ P108 GPIO0 / IO Camera 0 Power GPIO3_IO25 Enable, active low CAM0_PWR# output N4 ALT5 SAI5_RXFS__ P109 GPIO1 / IO Camera 1 Power GPIO3_IO19 Enable, active low CAM1_PWR# output L5 ALT5 SAI5_RXC__ P110 GPIO2 / IO Camera 0 Reset, active ...

- Page 132 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name P121 I2C_PM_CK E7 ALT0 I2C1_SCL__ IO OD Power management I2C1_SCL I2C bus clock P122 I2C_PM_DAT IO OD E8 ALT0 I2C1_SDA__ Power management I2C1_SDA I2C bus data P123 BOOT_SEL0# P5 ALT0 GPIO1_IO04__ I SYSBOOT and Line GPIO1_IO4 De‐multiplexer Logic Pulled up on Module. Driven by OD part on ...

- Page 133 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name P127 RESET_IN# I Reset input from Carrier board. Carrier drives low to force a Module reset, floats the line otherwise Pulled up on Module. Driven by OD part on Carrier. P128 POWER_BTN# I Power‐button input from carrier board. Carrier to float the line in in‐active state. Active low, level sensitive. It is de‐bounced on the Module Pulled up on Module. Driven by OD part on Carrier. D7 ALT0 UART4_TXD__ P129 ...

- Page 134 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name P136 SER2_TX D6 ALT0 UART2_TXD__ Asynchronous serial port data out UART2_DCE_TX P137 SER2_RX B6 ALT0 UART2_RXD__ Asynchronous serial port data in UART2_DCE_RX P138 SER2_RTS# E5 ALT5 ECSPI2_MOSI__ Request to Send GPIO5_IO11 handshake line for SER2 P139 SER2_CTS# C5 ALT5 ...

- Page 135 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name P147 VDD_IN P Power in P148 VDD_IN P Power in P149 VDD_IN P Power in P150 VDD_IN P Power in P151 VDD_IN P Power in P152 VDD_IN P Power in P153 VDD_IN P Power in P154 ...

- Page 136 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name S1 CS1_TX+/ F8 ALT0 I2C4_SCL__ IO Camera1 I2C bus I2C4_SCL I2C_CAM1_CK OD clock S2 CS1_TX‐/ F9 ALT0 I2C4_SDA__ IO Camera1 I2C bus I2C4_SDA I2C_CAM1_DAT OD data S3 GND P Ground S4 RSVD Not used ...

- Page 137 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name S17 GbE1_MDI0+ Not used S18 GbE1_MDI0‐ Not used S19 GbE1_LINK100# Not used S20 GbE1_MDI1+ Not used S21 GbE1_MDI1‐ Not used S22 GbE1_LINK1000# Not used S23 GbE1_MDI2+ Not used S24 GbE1_MDI2‐ Not used S25 GND P Ground S26 ...

- Page 138 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name S35 USB4+ Not used S36 USB4‐ Not used S37 USB3_VBUS_DET Not used S38 AUDIO_MCK H5 ALT0 SAI2_MCLK__ O Master clock output to SAI2_MCLK Audio codecs S39 I2S0_LRCK H4 ALT0 SAI2_TXFS__ IO Left& Right audio SAI2_TX_SYNC synchronization clock S40 I2S0_SDOUT ...

- Page 139 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name S48 I2C_GP_CK G8 ALT0 I2C3_SCL__ IO Port1 of TCA9546 I2C3_SCL OD General purpose I2C bus clock S49 I2C_GP_DAT E9 ALT0 I2C3_SDA__ IO Port1 of TCA9546 I2C3_SDA OD General purpose I2C bus clock S50 HDA_SYNC/ G3 ALT0 SAI3_TXFS__ IO Left& Right audio ...

- Page 140 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name S62 USB3_SSTX+ A13 USB1_TX_P AO USB3 data transmit signal differential pairs positive S63 USB3_SSTX‐ B13 USB1_TX_N AO USB3 data transmit signal differential pairs negative S64 GND P Ground S65 USB3_SSRX+ A13 USB1_TX_P AI USB3 data receive signal differential pairs positive ...

- Page 141 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name S76 PCIE_B_RST# H20 ALT5 NAND_CE3_B__ O Reset Signal for GPIO3_IO4 external devices. S77 PCIE_C_RST# Not used S78 PCIE_C_RX+ Not used S79 PCIE_C_RX‐ Not used S80 GND P Ground S81 PCIE_C_TX+ Not used S82 PCIE_C_TX‐ Not used ...

- Page 142 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name S90 PCIE_B_TX+ E25 PCIE2_TXN_P O Differential PCIe Link A transmit data pair 0 S91 PCIE_B_TX‐ E24 PCIE2_TXN_N O Differential PCIe Link A transmit data pair 0 S92 GND P Ground S93 DP0_LAN0+ Not used S94 DP0_LAN0‐ Not used S95 DP0_AUX_SEL Not used ...

- Page 143 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name S108 LVDS1_CK+ / O LVDS1 LCD eDP1_AUX+ differential clock / DSI1_CLK+ pairs S109 LVDS1_CK‐ / O LVDS1 LCD eDP1_AUX‐ / differential clock DSI1_CLK‐ pairs S110 GND P Ground S111 LVDS1_0+ / AIO LVDS1 LCD data eDP1_TX0+ / channel differential ...

- Page 144 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name S120 LVDS1_3+ / AIO LVDS1 LCD data eDP1_TX3+ / channel differential DSI1_D3+ pairs 4 S121 LVDS1_3‐ / AIO LVDS1 LCD data eDP1_TX3‐ / channel differential DSI1_D3‐ pairs 4 S122 LCD1_BKLT_ Not used PWM S123 RSVD Not used S124 GND P Ground S125 LVDS0_0+ / ...

- Page 145 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name S131 LVDS0_2+ / LVDS0 LCD data eDP0_TX2+ / channel differential DSI0_D2+ pairs 3 S132 LVDS0_2‐ / LVDS0 LCD data eDP0_TX2‐ / channel differential DSI0_D2‐ pairs 3 S133 LCD_VDD_EN K1 ALT5 SAI1_RXC__ O High enables panel GOIO4_IO1 VDD S134 LVDS0_CK+ / O LVDS0 LCD eDP0_AUX+ / differential clock ...

- Page 146 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name S139 I2C_LCD_CK G7 ALT0 I2C2_SCL__ IO LCD display I2C bus I2C2_SCL clock OD S140 I2C_LCD_DAT F7 ALT0 I2C2_SDA__ IO LCD display I2C bus I2C2_SDA clock OD S141 LCD_BKLT_PWM E6 ALT1 SPDIF_EXT_CLK__ O Display backlight PWM1_OUT PWM control ...

- Page 147 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name S147 VDD_RTC P Low current RTC circuit backup power ‐ 3.0V nominal It is sourced from a Carrier based Lithium cell or Super Cap S148 LID# M6 ALT0 GPIO1_IO09__ I Lid open/close GPIO1_IO9 indication to Module. Low indicates lid closure (which system may use to initiate a sleep state). Carrier to float the line in in‐active state. Active low, level sensitive. Should be de‐bounced on the Module Pulled up on Module.

- Page 148 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name S150 VIN_PWR_BAD# I Power bad indication from Carrier board. Module and Carrier power supplies (other than Module and Carrier power supervisory circuits) shall not be enabled while this signal is held low by the Carrier. Pulled up on Module. Driven by OD part on Carrier. S151 CHARGING# T7 ALT0 GPIO1_IO01__ I Held low by Carrier if GPIO1_IO1 DC input for battery charger is present. Pulled up on Module. Driven by OD part on ...

- Page 149 Embedian, Inc. SMARC Edge Finger NXP i.MX8M CPU Type Description Pin# Pin Name Ball Mode Signal Name S154 CARRIER_PWR_ON O Carrier board circuits (apart from power management and power path circuits) should not be powered up until the Module asserts the CARRIER_PWR_ON signal. S155 FORCE_RECOV# I Pulled up on Module. Driven by OD part on Carrier. S156 BATLOW# N7 ALT0 GPIO1_IO08__ I Battery low GPIO1_IO8 indication to Module. Carrier to float the line in in‐active state.

- Page 150 Embedian, Inc. Power Control Signals between SMARC Module and Carrier This Chapter points out the handshaking rule between SMARC module and carrier. Section include: SMARC‐iMX8M Module Power Power Signals Power Flow and Control Signals Block Diagram Power States Power Sequences Terminations Boot Select SMARC-iMX8M Computer on Module User’s Manual v.1.0...

-

Page 151: Chapter 4 Power Control Signals Between Smarc-Imx8M Module And Carrier

Embedian, Inc. Chapter 4 Power Control Signals between SMARC‐iMX8M Module and Carrier SMARC modules are designed to be driven with a single +3V to +5.25V input power rail. Unlike Q7 module, there is no separate voltage rail for standby power, other than the very low current RTC voltage rail. All module operating and standby power comes from the single set of VDD_IN pins. This suits battery power sources well, and is also easy to use with non‐battery sources. SMARC module has specific handshaking rules to the carrier by SMARC ... - Page 152 Embedian, Inc. 4.1.2. No Separate Standby Voltage There is no separate voltage rail for standby power, other than the very low current RTC voltage rail. SMARC‐iMX8M operating and standby power comes from the single set of VDD_IN pins. This suits battery power sources well, and is also easy to use with non‐battery sources. 4.1.3. RTC/Backup Voltage RTC backup power is brought in on the VDD_RTC rail. The RTC consumption is typically 15 microA or less. The allowable VDD_RTC voltage range shall be 2.0V to 3.25V. The VDD_RTC rail is sourced from a Carrier based Lithium cell, or it may be left open if the RTC backup functions are not required. SMARC‐iMX8M module is able to boot without a VDD_RTC voltage source. Lithium cells, if used on Carrier, shall be protected against charging by a ...

- Page 153 Embedian, Inc. module through IO lines and disturbs the SMARC module power on sequence. More seriously, it might cause to the CPU won’t boot up. It is always recommended that the power on module has to be earlier than that on carrier board. The boot up of module depends on when you release the reset signal of ...

- Page 154 Embedian, Inc. Module and Carrier power supplies (other than Module and Carrier power supervisory circuits) will not be enabled while this signal is held low by the Carrier. This signal has a 100K pull‐up on module and is driven by OD part on Carrier. 4.1.8. System Power Domains It is useful to describe an SMARC system as being divided into a hierarchy of three power domains: 1) Battery Charger power domain (can be neglected if the system is not battery powered only) 2) SMARC Module power domain 3) Carrier Circuits power domain The Battery Charger domain includes circuits that are active whenever either charger input power and / or battery power are available. These ...

- Page 155 Embedian, Inc. Module Power Domain Battery Charger Power Domain CHARGER_PRSNT# CHARGER INPUT CHARGING# BATLOW# BATTERY POWER 3.0 to 5.25V SMARC CHARGER Module I2C_PM I2C_PM BATTERY (Optional) 1.8V OUT EEPROM Carrier Power Supplies should not Come up before assertion of CARRIER_PWR_ON...

-

Page 156: Power Signals

Embedian, Inc. 4.2 Power Signals 4.2.1. Power Supply Signals SMARC Edge Finger Type Power Rail Description Pin# Pin Name 1 P147, P148, P149, VDD_IN I 3.0V~5.25V Main power supply input P150, P151,P152, for the module P153, P154, P155, P156 P2, S3, P9, S10, P12, GND I Common signal and S13, P15, S16, P18, power ground S25, P32, S34, P38, S47, P47, P50, P53, P59, S61, S64, S67, P68, S70, S73, P79, S80, P82, S83, P85, S86, P88, S89, P91, S92, P94, P97, P100, S101, P103, S110, S119, P120, S124, S130, P133, S136, P142, S143, S158 S147 VDD_ ... - Page 157 Embedian, Inc. 4.2.2. Power Control Signals The input pins listed in the following table are all active low and are meant to be driven by OD (open drain) devices on the Carrier. The Carrier either floats the line or drives it to GND. No Carrier pull‐ups are needed. The pull‐up functions are performed on the Module. The voltage rail that these lines are pulled to on the Module varies, depending on the design, and may be 3.3V or VDD_IN. SMARC Edge Finger I/O Type Power ...

- Page 158 Embedian, Inc. 4.2.3. Power Management Signals The pins listed in the following table are related to power management. They will be used in a battery‐operated system. SMARC Edge Finger I/O Type Power Description Rail Pin# Pin Name S156 BATLOW# I CMOS VDD_IO Battery low indication to Module. Carrier to float the line in in‐active state. Pulled up on Module. Driven by OD part on Carrier. S154 CARRIER_PWR_ON O CMOS ...

- Page 159 Embedian, Inc. SMARC Edge Finger I/O Type Power Description Rail Pin# Pin Name S151 CHARGING# I Strap VDD_IO Held low by Carrier during battery charging. Carrier to float the line when charge is complete. Pulled up on Module. Driven by OD part on Carrier. S149 SLEEP# I CMOS VDD_IO Sleep indicator from Carrier board. May be sourced from user Sleep button or Carrier logic. Carrier to float the line in in‐active state. Active low, level sensitive. Should be de‐bounced on the Module. Pulled up on Module. Driven by OD part on Carrier. S148 LID# I CMOS VDD_IO Lid open/close indication to ...

- Page 160 Embedian, Inc. 4.2.4. Special Control Signals (TEST#) i.MX8M processor does not support to boot up from SPI NOR flash. SMARC‐iMX8M module boots up from the onboard eMMC Flash first. The firmware in the eMMC flash will read the BOOT_SEL configuration and decides where to load the u‐boot. In some situations like the firmware in eMMC flash needed to be ...

-

Page 161: Power Flow And Control Signals Block Diagram

Embedian, Inc. 4.3 Power Flow and Control Signals Block Diagram Following figures shows the power flow and control signals block diagram. Figure 27: Power Block Diagram SMARC-iMX8M Computer on Module User’s Manual v.1.0... - Page 162 Embedian, Inc. When main power is supplied from the carrier, a voltage detector will assert VIN_PWR_BAD# signal to tell the module and carrier that the power is good. This signal will turn on the PMIC on module to power on the module. Carrier power circuits in the carrier Power domain should not power up unless the module asserts CARRIER_PWR_ON. The module signal CARRIER_PWR_ON exists to ensure that the module is powered before the main body of carrier circuits (those outside the power and power control path on the carrier). The main body of carrier board circuits will not be powered until the module asserts the CARRIER_PWR_ON signal being correct. Module hardware will assert CARRIER_PWR_ON when all power supplies necessary for module ...

-

Page 163: Power States

Embedian, Inc. 4.4 Power States The SMARC‐iMX8M module supports different power states. The table below describes the behavior in the different states and which power rails and peripherals are active. Additional power states can be implemented if required using available GPIOs to control additional power domains and peripherals. Abbr. Name Description Module Carrier Board UPG Unplugged No power is applied No main VDD_IN No power supply to the system, applied from fixed DC input, RTC battery except the RTC supply, VDD_IN maybe inserted battery might be available if backup available battery is implemented OFF ... - Page 164 Embedian, Inc. suspend by software. There might be different wake up sources available. Consult the datasheet for SMARC‐iMX8M module for more information about the available wakeup events. In the running state, a shutdown request can be triggered by software. This turns off all power rails on the module and requests the carrier board to ...

-

Page 165: Power Sequences

Embedian, Inc. 4.5 Power Sequences When main power is supplied from the carrier, a voltage detector will assert VIN_PWR_BAD# signal to tell the module and carrier that the power is good. This signal will enable the PMIC on module to power on the module. The module will not power up if the module receives a low‐active VIN_PWR_BAD# signal. The SMARC‐iMX8M module starts asserting CARRIER_PWR_ON as soon as the main voltage supply being applied to the module and all power supplies ... - Page 166 Embedian, Inc. Figure 29: Power‐Up Sequence If the operating system supports it, a shutdown sequence can be initiated. Some systems may benefit from shutting down instead of just removing the main power supply as this allows the operating system to take care of any ...

- Page 167 Embedian, Inc. Figure 30: Shutdown Sequence SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 168 Embedian, Inc. When the RESET_IN# is asserted, a reset cycle is initiated. The module internal reset and the external reset output RESET_OUT# are asserted as long as RESET_IN# is asserted. If the reset input RESET_IN# is de‐asserted, the internal reset and the RESET_OUT# will remain low for at least 1ms until they are also de‐asserted and the module starts booting again. This guarantees a minimum reset time of 1ms even if the reset input RESET_IN# is triggered for a short time. Figure 31: Reset Sequence SMARC-iMX8M Computer on Module User’s Manual v.1.0...

-

Page 169: Terminations

Embedian, Inc. 4.6 Terminations 4.6.1. Module Terminations The Module signals listed below will be terminated on the Module. The terminations follow the guidance given in the table below. Signal Name Series Termination Parallel Termination Notes HDMI_CTRL_DAT 1.5k pull‐up to 1.8V Carrier pull‐up required HDMI_CTRL_CK 1.5k pull‐up to 1.8V Carrier pull‐up required PCIE_[A:B]_TX+ 0.2uF Capacitor PCIE_[A:B]_TX‐ 0.2uF Capacitor I2C_PM_DAT 2.2K pull‐up to 1.8V I2C_PM_CK 2.2K pull‐up to 1.8V I2C_LCD_DAT 2.2K pull‐up to 1.8V I2C_LCD_CK ... - Page 170 Embedian, Inc. Signal Name Series Termination Parallel Termination Notes USB[0:3]_EN_OC# 10K pull‐up to 3.3V or x is ‘0’ or ‘1’ a switched 3.3V on the Switched 3.3V: if a Module USB channel is not used, then the USBx_EN_OC# pull‐up rail may be held at GND to prevent leakage currents. VIN_PWR_BAD# 200k pull‐up to VIN USB[2:3]_SSTX+ 0.2uF Capacitor USB[2:3]_SSTX‐ 0.2uF Capacitor SMARC-iMX8M Computer on Module User’s Manual v.1.0...

- Page 171 Embedian, Inc. 4.6.2. Carrier/Off‐Module Terminations The following Carrier terminations are required, if the relevant interface is used. If unused, the SMARC Module pins may be left un‐connected. Module Signal Carrier Series Carrier Parallel Notes Group Name Termination Termination GBE_MDI Magnetics module Secondary side center tap appropriate for terminations appropriate 10/100/1000 GBE for Gigabit Ethernet transceivers implementations GBE_LINK If used, current limiting The open drain resistors and diodes to GBE status (GBE status LED pulled to a positive supply signals, sinks) ...