Table of Contents

Advertisement

Quick Links

.

FULLY PROGRAMMABLE TIMING GENER-

.

ATOR

ALPHANUMERIC AND GRAPHIC DRAWING

.

CAPABILITY

EASY TO USE AND POWERFUL COMMAND

SET :

- VECTOR, ARC, CIRCLE WITH DOT OR

PEN CONCEPT AND PROGRAMMABLE

LINE STYLE,

- FLEXIBLE AREA FILL COMMAND WITH

TILING PATTERN,

- VERY FAST BLOCK MOVE OPERATION,

- CHARACTER DRAWING COMMAND, ANY

.

SIZE AND FONTS AVAILABLE

LARGE FRAME

BUFFER

SPACE (8 megabytes) UP TO 16 PLANES OF

.

2048 x 2048

.

UP TO 256 COLOR CAPABILITIES

MASK BIT PLANES FOR GENERAL CLIP-

.

PING PURPOSE

FRAME BUFFER CAN BE BUILT WITH

STANDARD 64 K OR 256 K DRAM OR DUAL-

.

PORT-MEMORIES (video-RAM)

EXTERNAL SYNCHRONIZATION CAPABIL-

.

ITY

ON CHIP VIDEO SHIFT REGISTERS FOR

.

DOT RATE UP TO 18 MEGADOTS/S

8 OR 16-BIT BUS INTERFACE COMPATIBLE

WITH MARKET STANDARD MICROPROC-

.

ESSORS

.

HMOS 2 TECHNOLOGY

.

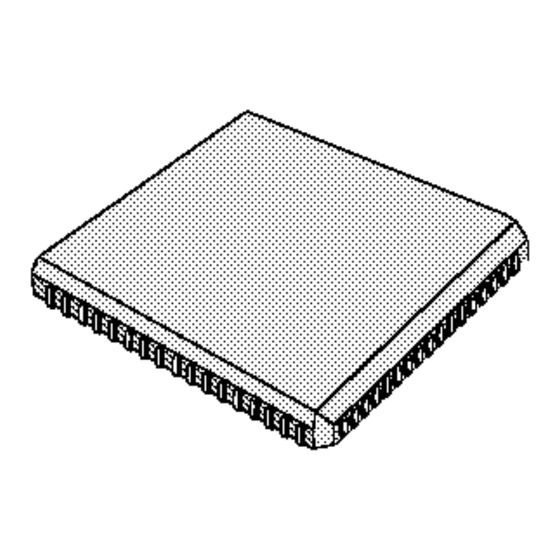

68 - PIN PLCC PACKAGE

FOR DETAILED INFORMATION, REFER TO

TS68483 USER'S MANUAL

DESCRIPTION

The TS68483 is an advanced color graphic proc-

essor that drastically reduces the CPU software

overhead for all graphic tasks in medium and high

range graphic applications such as business and

personal computer, industrial monitoring system

and CAD systems.

September 1993

HMOS2 ADVANCED GRAPHIC

AND ALPHANUMERIC CONTROLLER

ADDRESSING

PIN CONNECTIONS

D4

D5

D6

D7

D8

D9

D10

D11

D12

Vss

NC

NC

D13

D14

D15

CS

DS

TS68483A

PLCC68

(Plastic Chip Carrier)

ORDER CODE : TS68483A

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

60

ADM15

59

ADM14

58

ADM13

57

ADM12

56

ADM11

55

ADM10

54

ADM9

53

ADM8

52

Vcc

51

ADM7

50

ADM6

49

ADM5

48

ADM4

47

ADM3

46

ADM2

45

ADM1

44

ADM0

1/30

Advertisement

Table of Contents

Summary of Contents for SGS TS68483A

- Page 1 (Plastic Chip Carrier) LARGE FRAME BUFFER ADDRESSING SPACE (8 megabytes) UP TO 16 PLANES OF ORDER CODE : TS68483A 2048 x 2048 UP TO 256 COLOR CAPABILITIES MASK BIT PLANES FOR GENERAL CLIP- PING PURPOSE FRAME BUFFER CAN BE BUILT WITH...

-

Page 2: Pin Description

TS68483A PIN DESCRIPTION Name Type Function Description MICROPROCESSOR INTERFACE D (0 : 15) Data Bus These sixteen bidirectional pins provide communication with either an 8 or 16-bit host microprocessor data bus. A (0 : 7) Address Bus These eigth pins select the internal register to be accessed. The address can be latched by AE for direct connection to address/data multiplexed microprocessor busses. -

Page 3: Block Diagram

TS68483A BLOCK DIAGRAM MICROPROCESSOR INTERFACE AE, DS D [0: 15] A [0:7] R/W, CS PC/HS HVS/VS VIDEO VIDEO SYNC IN INTERFACE TIMING GENERATOR DRAWING VIDEO P [0:3] SHI FT ACCESS REGISTERS PROCESSOR DATA DATA DISPLAY MEMORY LOGIC CYF [0:1] B [0:1]... -

Page 4: Electrical Characteristics

TS68483A ELECTRICAL CHARACTERISTICS = 5.0 V ± 5 %, V = 0, T to T ) (unless otherwise specified) Symbol Parameter Min. Typ. Max. Unit Supply Voltage 4.75 5.25 Input Low Voltage – 0.3 Input High Voltage µA Input Leakage Current = –... - Page 5 TS68483A of lines per field (up to 1024). The address of the MEMORY ADDRESS : (see Figure 3). display viewport (this part of the display memory to In order to address one bit in the display memory, be actually displayed on the screen) is fully pro- the user must specify : grammable.

- Page 6 TS68483A Figure 2 : Cyclical Drawing Coordinates to Display Memory Mapping BANK3 BANK 1 MASK BANK 0 BITS LONG PELS SHORT PELS Figure 3 : The Display Memory Addressing Space BANK 0 BANK 1 BANK 2 BANK 3 THE MEMORY WORD...

- Page 7 TS68483A Table 1 : Command Set Structure Command Drawing Mode Type Group Line Up to the Pen Linear Rectangle Monochrome Area Trapezium Drawing Polygon Polyarc Print Char Bichrome Cell Print Object Polychrome Load Viewport Access Save Viewport Management Modify Viewport...

- Page 8 TS68483A Figure 4 : Pointers Bank number 13-bit positive value address DESTINATION Plane number 13-bit positive value POINTER Sign Absolute value Sign Absolute value Byte Bank number 11-bit positive value address SOURCE Character cell plane (PCA) 8-bit positive value POINTER...

- Page 9 TS68483A In other words : short pels are used, any bank may hold a frame - When the destination mask use (DMU) parame- buffer. In this case, the bank parity selects the color ter is set : nibble used. (See destination pointer section for - a pel may be modified when its mask bit is set bank addressing).

- Page 10 TS68483A - a color transform and a mask transform for the set is defined by the cell dimensions (DXs, DYs). BACKGROUND PELS Note : when the cell is an object, SMU is not programmable and is implicitly set. A calculated II4.5 - POLYCHROME MODE...

- Page 11 TS68483A II.4.7 - SCALING FACTOR AND CELL MAPPING : PRINT CHARACTER, PRINT OBJECT and LIN- (see Figures 9 and 10) EAR commands when the pen is a cell. The AREA or ACCESS or LINEAR (DOT) commands are Figure 9 : Scaling Factor never scaled.

- Page 12 TS68483A II.5 - Command Set Overwiew Note : an underlined cell is drawn when the MSB of R23 is set. Figure 11 II.5.4 - ACCESS COMMANDS - LOAD VIEWPORT (Xs, Ys, DXs, DYs) - SAVE VIEWPORT (Xs, Ys, DXs, DYs)

-

Page 13: Microprocessor Interface

TS68483A Figure 12 : Status Register lar 8 or 16-bit host microprocessor ; either Motorola type (6809, 68008, 68000) or Intel type (8088, 15 14 13 12 11 10 8086). STATUS REGISTER R12 The host microprocessor has direct access to any... - Page 14 TS68483A Figure 14 : Interface with TS68000/68008MPU TS68000 TS68483 D [8:15] D [8:15] D [0:7] D [0:7] A [1:7] A [1:7] UDS or LDS TS68008 TS68483 D [8:15] D [0:7] D [0:7] A [1:7] A [1:7] Figure 15 : Interface with 8086/8008 MPU...

- Page 15 TS68483A III.2 - Hardware Recommendations AE, DS, R/ W, CS : See pin description. (see Figures 21, 22, 23 and 24) III.3 - SOFTWARE RECOMMENDATIONS A0-PIN : 1. The CONFIGURATION register R10 must be 1. When using a 16-bit data bus, the A0 input pin first initialized.

- Page 16 TS68483A IV.2.4. MEMORY TIME SHARING (see Figure 16) Figure 16 : Video Programming HORIZONTAL BLKX FRONT BACK BLKY PORCH DWX DISPLAY PORCH Horizontal Minimum Number of Cycles FRONT BLANKING PORCH MARGIN DISPLAY DISPLAY BACK PORCH = BPY - 25 25 Lines...

- Page 17 TS68483A IV.3.1 - Y ADDRESSES IV.3.4 - PAN AND TILT When INE = 0, the fields are not interlaced. The Y The host can tilt or pan the Display Viewport Display Viewport address is initialized with YOR at through the frame buffer by modifying YOR or XOR the first displayable line then decremented by 1 at arguments.

-

Page 18: Memory Organization

TS68483A Table 4 Number Mininmum Name Register Description Function of Bits Values Number of Display lines per Field Interlace Enable when INE = 1 Vertical Number of Lines in Vertical Blanking – 2.5 Scan Number of Lines in Vertical Front Porch Number of Lines in Vertical Back Porch + 2.5... - Page 19 TS68483A or up to 8 bits per pixel are required, the designer - RAD and CAD Enable signals to the Mapper. must provide external shift registers. Video RAM V.3.1 - FRAME BUFFER (see Table 6) components may also be considered.

- Page 20 TS68483A Figure 17 : One Block - One Z ADM [8:15] ADM [0:7] 8 (T1) 8 (T0) 8 (T1) 8 (T0) Figure 18 : One Block - Two Z ADM [8:15] ADM [0:7] (T0. T1) = Page mode Figure 19...

-

Page 21: Timing Diagram

TS68483A Figure 20 : Memory Organization for 512 x 384 Application ADM [8:15] B [0:1] Y [0:2] ADM [0:7] LATCH BANK ENABLE CYCLE CAD0 CONTROLLER ADSEL DATA DATA Z1/Z3 Z0/Z2 64K x 8 64K x 8 MEMORY ADDRESS 64K x 8... - Page 22 TS68483A Figure 21 : Read Cycle A [0:7] AS (MPU) DATA OUT D [0:15] Figure 22 : Write Cycle A [0:7] AS (MPU) DATA IN D [0:15] 22/30...

-

Page 23: Mux Mode

TS68483A MUX MODE Microprocessor Interface Timing : A (0 : 7), D (0 : 15), AE, DS, CS, R/W = 5.0V ± 5 %, T to T = 10 pF on D (0 : 15) Reference Levels : V = 0.8V and V = 2V on All Inputs, V = 0.4V and V... -

Page 24: Fast Write

TS68483A Figure 23 : Read Cycle Figure 24 : Write Cycle FAST WRITE 24/30... - Page 25 TS68483A VI.2 - Memory Interface ADM (0 : 15), B (0 : 1), CYF (0 : 1), Y (0 : 2), CYS = 5.0V ± 5 %, T to T , CLK Duty Cycle = 50 %, Period T Reference Levels : V = 0.8V and V...

- Page 26 TS68483A VI.3 - Video Interface P0, P1, P2, P3, BLK, HVS/VS, PC/HS = 5.0V ± 5 %, T to T , CLK duty cycle = 50% Reference levels : V = 0.8V and V = 2V, V = 0.4V and V = 2.4V, C...

- Page 27 TS68483A VII - TABLES VII.1 - Register Map and Command Table Figure 28 COMMAND MODE Odd Bank Even Bank Odd Bank Even Bank TEXLIN DIB1 DIB0 MARGIN COLOR MODX1 MODX0 VSIE HSIE NBLK NHVS NPC SYNC STATUS STOP : Don’t care...

- Page 28 TS68483A VII.2. Command Table 28/30...

- Page 29 TS68483A Figure 29 : Typical Application HOST SYSTEM MICROPROCESSOR MEMORY 8 OR 16 BITS SYNC SYNC TS68483 CRT CONTROLLER MONITOR DISPLAY MEMORY INTERFACE DISPLAY MEMORY 29/30...

- Page 30 No licence is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics.

Need help?

Do you have a question about the TS68483A and is the answer not in the manual?

Questions and answers