Summary of Contents for Texas Instruments TMS320C6201

- Page 1 TMS320C6201 Digital Signal Processor Silicon Errata SPRZ153 November 2000 Copyright 2000, Texas Instruments Incorporated...

-

Page 2: Table Of Contents

................Changes to the TMS320C6201 Data Sheet (literature number SPRS051) . - Page 3 TMS320C6201 Silicon Errata SPRZ153 Advisory 2.1.19 PMEMC: Branch from External to Internal ..........

-

Page 4: Introduction

Quality and Reliability Conditions TMX Definition Texas Instruments (TI) does not warranty either (1) electrical performance to specification, or (2) product reliability for products classified as “TMX.” By definition, the product has not completed data sheet verification or reliability performance qualification according to TI Quality Systems Specifications. -

Page 5: Revision Identification

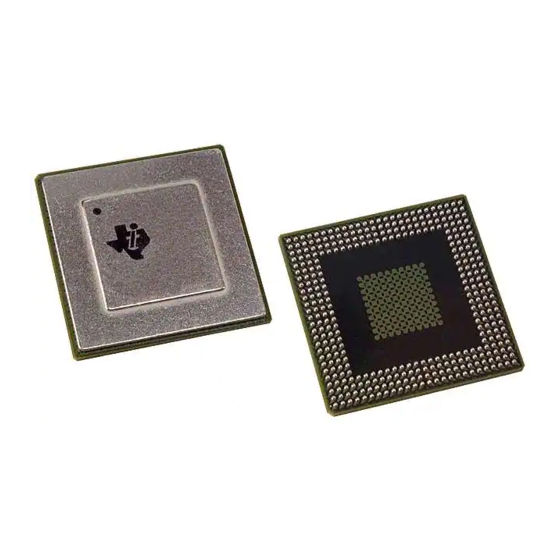

The device revision can be determined by the lot trace code marked on the top of the package. The location for the lot trace codes for the GJL package is shown in Figure 1 and the revision numbers are listed in Table 1. Figure 1. Example, Lot Trace Code for TMS320C6201 TMS320C6201GJL TMS320C6201GJL Cxx–YMLLLLS... -

Page 6: Changes To The Tms320C6201 Data Sheet (Literature Number Sprs051)

TMS320C6201 Silicon Errata SPRZ153 Changes to the TMS320C6201 Data Sheet (literature number SPRS051) Table 2. Timing Requirements for Interrupt Response Cycles C6201B UNIT UNIT t d(CKO2L-IACKV) Delay time, CLKOUT2 low to IACK valid –4 t d(CKO2L-INUMV) Delay time, CLKOUT2 low to INUMx valid... - Page 7 TMS320C6201 Silicon Errata SPRZ153 Figure 3. SBSRAM Write Timing (1/2 Rate SSCLK) (See Note) SSCLK BE_ [3:0] EA [21:2] ED [31:0] SSADS SSOE SSWE NOTE: The CEx output setup and hold times are specified to be accurate relative to the clock cycle to which they are referenced, since these timings are specified as minimums.

-

Page 8: Silicon Revision 3.1 Known Design Exceptions To Functional Specifications

TMS320C6201 Silicon Errata SPRZ153 Silicon Revision 3.1 Known Design Exceptions to Functional Specifications Advisory 3.1.1 Issues When Pausing at a Block Boundary Revision(s) Affected: 3.1, 3.0, 2.1, and 2.0 Details: The following problems exist when a DMA channel is paused at a block boundary: DMA does not flush internal FIFO when a channel is paused across block boundary. -

Page 9: Advisory 3.1.3

TMS320C6201 Silicon Errata SPRZ153 Advisory 3.1.3 DMA Multiframe Split-mode Transfers Source Address Indexing Not Functional Revision(s) Affected: 3.1, 3.0, 2.1, and 2.0 Details: If a DMA channel is configured to do a multiframe split-mode transfer with SRC_DIR = Index (11b), the source address is always modified using the Element Index, even during the last element transfer of a frame. -

Page 10: Advisory 3.1.6

TMS320C6201 Silicon Errata SPRZ153 Advisory 3.1.6 DMA Paused During Emulation Halt Revision(s) Affected: 3.1, 3.0, 2.1, and 2.0 Details: When running an autoinitialized transfer, the DMA write state machine is halted during an emulation halt regardless of the value of EMOD in the DMA Channel Primary Control Register. -

Page 11: Advisory

TMS320C6201 Silicon Errata SPRZ153 Alternative: If a 64M-bit SDRAM is located in CE3, avoid using the last 1K byte in the CE3 memory map (0x03FFFC00). Advisory 3.1.9 Cache During Emulation With Extremely Slow External Memory Revision(s) Affected: 3.1, 3.0, 2.1, and 2.0 Details: If a program requests fetch packet “A”... -

Page 12: Silicon Revision 3.0 Known Design Exceptions To Functional Specifications

TMS320C6201 Silicon Errata SPRZ153 Silicon Revision 3.0 Known Design Exceptions to Functional Specifications Advisory 3.0.8 EMIF: Inverted SDCLK and SSCLK at Speeds Above 175 MHz Revision(s) Affected: 3.0, 2.1, and 2.0 Details: A speedpath in the device causes SDCLK and SSCLK to start up 180 degrees out-of-phase (effectively inverted) from the desired waveform. - Page 13 (SSCLK to SDRAM and SDCLK to SBSRAM). This will cause invalid operation at frequencies below 175 MHz and will not work with future silicon revisions. If CLKOUT2 is used as an SDRAM clock, follow all the workarounds for SDCLK. C62x is a trademark of Texas Instruments Incorporated.

-

Page 14: Advisory 3.0.9

TMS320C6201 Silicon Errata SPRZ153 EMIF: Inverted SDCLK and SSCLK at Speeds Above 175 MHz (Continued) Alternate Workaround: The following alternate workarounds can help for certain board and layout configurations. Using faster (125 MHz or PC100) SDRAMs and/or SBSRAMs will reduce the chances of data corruption and/or increase the frequency at which reliable memory operation can be observed. -

Page 15: Silicon Revision 2.1 Known Design Exceptions To Functional Specifications

TMS320C6201 Silicon Errata SPRZ153 Silicon Revision 2.1 Known Design Exceptions to Functional Specifications Advisory 2.1.1 EMIF: CE Space Crossing on Continuous Request Not Allowed Revision(s) Affected: 2.1 and 2.0 Details: Any continuous request of the EMIF cannot cross CE address space boundaries. This condition can result in bad data read, or writing to the wrong CE. -

Page 16: Advisory 2.1.4

TMS320C6201 Silicon Errata SPRZ153 EMIF: SDRAM Invalid Access (Continued) Workaround: Avoid use of multiple CE spaces of SDRAM within a single refresh period. Advisory 2.1.4 DMA: RSYNC Cleared Late for Frame-synchronized Transfer Revision(s) Affected: 2.1 and 2.0 In a frame-synchronized transfer, RSYNC is only cleared after the beginning of last write transfer. - Page 17 TMS320C6201 Silicon Errata SPRZ153 McBSP: DXR to XSR Copy Not Generated (Continued) Example: Configure the DMA as follows: (a) For half-word/byte-size accesses with right justification on receive data: – ch_A: /* for transmit */ src_address = mem_out; dst_address = DXR;...

-

Page 18: Advisory 2.1.6

TMS320C6201 Silicon Errata SPRZ153 McBSP: DXR to XSR Copy Not Generated (Continued) (c) For byte-size writes with right justification on receive data: – ch_A: /* for transmit */ dst_address = DXR+3; /* 0x018C0007 for McBSP0 or 0x01900007 for McBSP1 */ Element_size = WORDAddress_inc_mode = indexIndex_reg_value = 1 –... -

Page 19: Advisory 2.1.8

TMS320C6201 Silicon Errata SPRZ153 Advisory 2.1.7 DMA Channel 0 Multiframe Split-Mode Incompletion Revision(s) Affected: 2.1 and 2.0 Details: If DMA Channel 0 is configured to perform a multiframe split-mode transfer, it is possible for the last element of the last frame of the Receive Read to not be transferred. After the last... -

Page 20: Advisory 2.1.11 Mcbsp: Incorrect Mlaw Companding Value

TMS320C6201 Silicon Errata SPRZ153 McBSP: Incorrect mLaw Companding Value Advisory 2.1.11 Revision(s) Affected: 2.1 and 2.0 The C6201 McBSP m-Law/A-Law companding hardware produces an incorrectly expanded m-Law Details: value. McBSP receives m-Law value 0111 1111, representing a mid-scale analog value. Expanded 16-bit data is 1000 0000 0000 0000, representing a most negative value. -

Page 21: Advisory 2.1.14 Emif: Hold Request Causes Problems With Sdram Refresh

TMS320C6201 Silicon Errata SPRZ153 Advisory 2.1.14 EMIF: HOLD Request Causes Problems With SDRAM Refresh Revision(s) Affected: 2.1 and 2.0 Details: If the HOLD interface is used in a system with SDRAM, there are some situations that are likely to occur. -

Page 22: Advisory 2.1.16 Dma Split-Mode Receive Transfer Incomplete After Pause

TMS320C6201 Silicon Errata SPRZ153 Advisory 2.1.16 DMA Split-mode Receive Transfer Incomplete After Pause Revision(s) Affected: 2.1 and 2.0 Details: If the DMA is performing a split-mode transfer and the channel is paused after all Transmit Reads in a frame are completed but before the Receive Reads are completed, then the Receive Transfer will not complete after the channel is restarted. -

Page 23: Advisory 2.1.19 Pmemc: Branch From External To Internal

TMS320C6201 Silicon Errata SPRZ153 Advisory 2.1.19 PMEMC: Branch from External to Internal Revision(s) Affected: 2.1 and 2.0 Details: The program flow is corrupted after branching from external memory to internal program memory when the following are true: CPU is executing from external memory A CPU stall occurs that holds the CPU until all pending program fetches complete. -

Page 24: Silicon Revision 2.0 Known Design Exceptions To Functional Specifications

TMS320C6201 Silicon Errata SPRZ153 Silicon Revision 2.0 Known Design Exceptions to Functional Specifications Advisory 2.0.1 Program Fetch: Cache Modes Not Functional Revision(s) Affected: Workaround: Use internal program memory in mapped mode. Advisory 2.0.2 Bootload: Boot from 16-Bit and 32-Bit Asynchronous ROMs Not Functional... -

Page 25: Advisory 2.0.5

TMS320C6201 Silicon Errata SPRZ153 Advisory 2.0.5 Data Access: Parallel Accesses to EMIF or Internal Peripheral Bus Location Sequenced Wrong Revision(s) Affected: Details: Parallel read and write accesses to the same EMIF or internal peripheral bus location are sequenced incorrectly when: A load and store are in the same execute packet and either –... -

Page 26: Advisory 2.0.9

TMS320C6201 Silicon Errata SPRZ153 Advisory 2.0.9 McBSP New Block Interrupt Does Not Occur for Start of Block 0 Revision(s) Affected: Details: When end-of-block interrupt is selected ((R/X)INTM=01b), McBSP new block interrupt does not occur at end of frame (i.e., before block 0). (Internal reference number 4357) Workaround: This interrupt is used when on-the-fly channel selection/enabling is being performed. -

Page 27: Advisory 2.0.13 Mcbsp: Xempty Stays Low When Dxr Written Late

TMS320C6201 Silicon Errata SPRZ153 Advisory 2.0.13 McBSP: XEMPTY Stays Low When DXR Written Late Revision(s) Affected: Details: XEMPTY goes low and stays low when DXR was written on either the last bit or next-to-last bit of the previous word being transferred to DX. (Internal Reference Number 3383) Advisory 2.0.14... -

Page 28: Advisory 2.0.19 Emif: Data Setup Times

2. Open the “Products” dialog box and choose “Digital Signal Processors” 3. Scroll to the “TMS320C6000tHighest Performance DSP Platform” and click on “TMS320C62x DSP Generation”. 4. Click on a device name and then click on the documentation type you prefer. TMS320C6000 and C62x are trademarks of Texas Instruments. - Page 29 IMPORTANT NOTICE Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.