Advertisement

Quick Links

Interfacing ispClock5600A with

Reference Clock Oscillators

August 2008

Application Note AN6079

Introduction

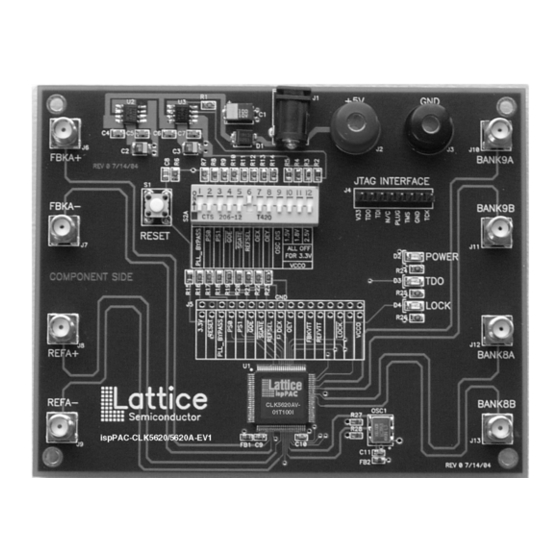

Lattice ispClock™5620A and ispClock5610A are in-system programmable zero delay clock generator ICs with inte-

grated universal fan-out buffers. In some applications these devices are required to generate multiple clock output

frequencies from a single reference oscillator clock source.

The input to output clock phase relation is guaranteed only when the reference clock high pulse width or low pulse

width are greater than the data sheet t

and t

specifications. If either specification is violated the

CLOCKHI

CLOCKLOW

input to output clock phase relationship can be restored by activation of the RESET pin of the ispClock 5600A

device. This application note examines two common conditions when the reference oscillator clock could violate

the t

or t

specifications and warrant the activation of the RESET pin.

CLOCKHI

CLOCKLOW

Powering Up Reference Oscillator After ispClock5600A

Figure 1 details the start-up behavior of a typical oscillator module. Note that for the first 50ms the output is active,

the amplitude and offset are ramping up. It is during this time that the ispClock may see a very narrow clock pulse

because the thresholds at the ispClock inputs are fixed but the oscillator output is changing. In this case the

RESET pin of the ispClock should be activated after the oscillator output is stable.

Figure 1. Powering Up a Reference Oscillator

Oscillator Enabled Asynchronously

Figure 2 shows the general behavior of a typical oscillator module when the output enable pin is controlled by an

asynchronous enable signal. The output is held low when the enable pin is low and oscillates when the enable pin

goes high. Figure 3 zooms in on the initial output transitions and reveals two short pulses that would result in a tim-

ing violation for the reference clock input of the ispClock.

© 2008 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand

or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

www.latticesemi.com

1

an6079_01.0

Advertisement

Summary of Contents for Lattice Semiconductor ispClock5620A

- Page 1 © 2008 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

- Page 2 Interfacing ispClock5600A Lattice Semiconductor with Reference Clock Oscillators Figure 2. CMOS Oscillator Enabled Figure 3. Initial Transitions of Enabled Oscillator In this case where the reference oscillator is gated on, either by the output enable pin of the oscillator or by other means of asynchronous enable, the RESET pin should be activated after the reference has been enabled and the clock input to the ispClock is stable.

- Page 3 Reference and Feedback MUXes The ispClock5620A has an input MUX for both the clock reference and the feedback inputs to the phase detect cir- cuitry. If the select line for either MUX is asynchronously changed then it may result in a timing violation similar to the waveforms shown in Figure 3.

- Page 4 Interfacing ispClock5600A Lattice Semiconductor with Reference Clock Oscillators Technical Support Assistance Hotline: 1-800-LATTICE (North America) +1-503-268-8001 (Outside North America) e-mail: isppacs@latticesemi.com Internet: www.latticesemi.com Revision History Date Version Change Summary August 2008 01.0 Initial release.