Table of Contents

Advertisement

Quick Links

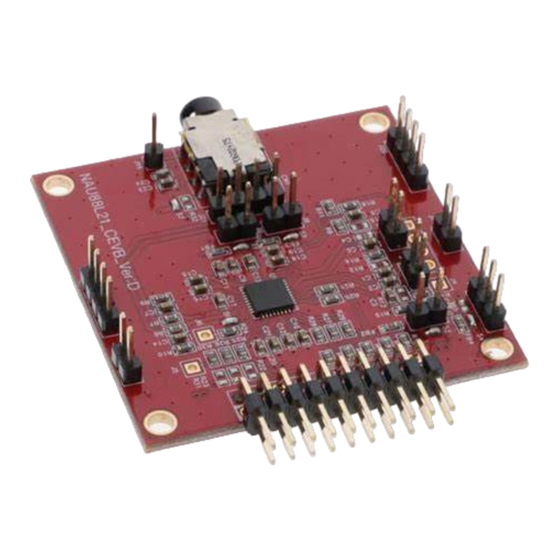

Ultra-Low Power Audio CODEC Ground-Referenced Headphone Amplifier

GENERAL DESCRIPTION

The NAU88L21 is an ultra-low power high performance audio codec that supports both analog and digital audio functions. It includes

one I2S/PCM interface, one digital microphone interface, one digital mixer, two high quality DACs and ADC's, and one stereo class

G headphone amplifier. The advanced on-chip signal processing engine that includes dynamic range compressor (DRC),

programmable biquad filter, as well as an integrated frequency locked loop (FLL) to support various input clocks.

FEATURES

DAC: 105dB SNR, (A-weighted) @ 0dB gain, 1.8V and -

88dB THD @ 20mW and RL= 32Ω, DAC playback to

headphone output mode

ADC: 103dB SNR (A-weighted) @ 0dB MIC gain, 1.8V, Fs

= 48kHz and -93dB THD, 1.8V, MIC gain 0dB, OSR 256x

1 Digital I2S/PCM I/O port

Two mono differential or one stereo differential analog

microphone inputs, two single-ended microphone inputs or

one stereo digital microphone input

Cap-free Low noise Microphone bias with 7uVrms noise

between 20Hz-20kHz, internal pull high resistor for

microphone.

Feb 28, 2022

Class G Headphone Amplifier (28mW @ 32Ω, 1%

THD+N)

Sampling rate from 8k to 192 kHz

Dynamic Range Compressor (DRC)Programmable Biquad

filter Integrated DSP with specific functions:Input

automatic level control (ALC/AGC)/limiter

Output dynamic-range-compressor/limiter

Package: 32 Pin QFN package

APPLICATIONS

Gaming controller

Wireless Headset

Smart Remote Controller

Page 1 of 78

NAU88L21

Rev 2.8

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for Nuvoton NAU88L21

- Page 1 GENERAL DESCRIPTION The NAU88L21 is an ultra-low power high performance audio codec that supports both analog and digital audio functions. It includes one I2S/PCM interface, one digital microphone interface, one digital mixer, two high quality DACs and ADC’s, and one stereo class G headphone amplifier.

-

Page 2: Block Diagram - Qfn32

Block Diagram - QFN32 VREF BIAS MICL+ MICL - ADC Effect Digital Audio DAC Effect Effects DMIC I / F Volume Volume Mixers MICR+ Programmable Sidetone Programmable MICR- BiQuad BiQuad MICBIAS MICBIAS CPOUTP VSSCP MICDET MICDET Charge CPOUTN I2 C Slave Pump Interface I2S/ PCM... -

Page 3: Table Of Contents

Table of Contents BLOCK DIAGRAM - QFN32 ..............2 PIN DIAGRAM ................... 6 PIN DESCRIPTION ..................7 ELECTRICAL CHARACTERISTICS ............8 GENERAL DESCRIPTION ..............11 Inputs ....................... 11 Outputs ......................11 ADC, DAC and Digital Signal Processing ............11 Digital Interfaces ....................11 POWER SUPPLY ................ - Page 4 Companding ....................27 5.6.1 µ-law ..............................27 5.6.2 A-law ..............................27 CLOCKING AND SAMPLE RATES ..........28 I2S/PCM Clock Generation ................29 Frequency Locked Loop(FLL) ................31 CONTROL INTERFACES ..............33 2-Wire-Serial Control Mode (I C Style Interface) ..........33 2-Wire Protocol Convention ................

- Page 5 12. PACKAGE INFORMATION .............. 73 13. REVISION HISTORY ................ 77 IMPORTANT NOTICE ................78 Feb 28, 2022 Page 5 of 78 Rev 2.8...

-

Page 6: Pin Diagram

Pin Diagram MICDET MICBIAS BITCLK VDDMIC MCLK QFN 32-pin VREF VDDA VSSA VSSD VDDA VDDB CPOUTP SCLK VSSCP SDIO Feb 28, 2022 Page 6 of 78 Rev 2.8... -

Page 7: Pin Description

Pin Description Pin # Name Type Functionality MICDET Analog IO Microphone/button detect, 2kOhm between Mic and Mic Bias MICBIAS Analog Output Microphone Bias Output VDDMIC Supply Microphone supply VREF Analog I/O Internal DAC & ADC voltage reference decoupling I/O VSSA Ground Analog Ground VDDA... -

Page 8: Electrical Characteristics

Electrical Characteristics Conditions: V A = V B = 1.8V; V MIC= 3.6V. (Headphone) = 32 Ω, f = 1kHz, MCLK=12.88MHz, unless otherwise specified. Limits apply for T = 25°C Symbol Parameter Conditions Typical Limit Units Shutdown Current µA Headset Detection Standby MCLK off, Jack Insertion, IRQ enabled µA Mode... - Page 9 Symbol Parameter Conditions Typical Limit Units = 48kHz, Stereo DAC On, Amp On, 32Ω = 0mW. R Fs Accuracy (44.1 / 48 kHz) 0.02% Pop and Click Noise plug Into or out of DAC to Headphone mVrms MIC Input, MIC_GAIN = 0dB, VIN = 0.8Vrms, f=1020Hz, fs = 48KHz, Mono Differential Input ADC Total Harmonic Distortion +...

- Page 10 Recommended Operating Conditions Condition Symbol Typical Units Digital I/O Supply Range 1.62 Analog Supply Range 1.62 1.98 Headphone Supply Range 1.62 1.98 Microphone Bias Supply Voltage Temperature Range °C Absolute Maximum Ratings Parameter Units Digital Supply Range -0.3 Digital I/O Supply Range -0.3 Analog Supply Range -0.3...

-

Page 11: General Description

The channel has a fully differential programmable gain amplifier (PGA). The outputs of the PGA connect to the ADC. The NAU88L21 also has an input for one digital microphone. The NAU88L21 provides a DMCLK, the clock signal for the digital microphones. -

Page 12: Power Supply

2.1 Power on and off reset The NAU88L21 includes a power on reset circuit on chip. The circuit resets the internal logic control at VDDA supply power up and this reset function is automatically generated internally when power supplies are too low for reliable operation. -

Page 13: Input Path Detailed Descriptions

3. Input Path Detailed Descriptions NAU88L21 has two low noise, high common mode rejection ratio analog microphone differential input. The microphone inputs MICL+/- & MICR+/- which are followed by -1dB to 36dB PGA gain stages that have a fixed 12kOhm input impedance. -

Page 14: Digital Microphone Input

MICL- is the data in 3.3 VREF The NAU88L21 includes a mid-supply reference circuit that produces a voltage close to VDDA/2. This “VREF” pin should be decoupled to VSS through an external bypass capacitor. Because VREF is used as a reference voltage inside the NAU88L21, a large capacitance is required to achieve good power supply rejection at low frequency. -

Page 15: Mic Bias

Circuitry 3.4 MIC Bias The NAU88L21 provides one MIC bias pin, which can be used to power various microphones. The output level of MIC Bias can be set between VDDA and 1.53 X VDDA using register settings. It is recommended that the microphones do not draw more than 4mA from the MICBIAS pin. There are options for connecting internal 2 Kohm resistor to the microphone and for low noise or low power mode. - Page 16 MicBias MICBIAS MICDET Mic Detect MicDet Button Detect Figure 4. Mic Detect and MICBIAS blocks Application note: Adding a simple RC on the MICDET pin can help reduce noise coupling. These may be board level related, or component related effects. Figure 5.

-

Page 17: Key Release

3.5.1 Key Release This feature detects the edge case where the key press interrupt is not followed by a release interrupt until later on in the sequence and clears the x11 register to prepare for further interrupts. Write Register x11 Wait for Key Release to Clear... -

Page 18: Adc Digital Block

4.1.1 Level Estimation The NAU88L21 uses Peak level estimation that depends on the attack and decay time settings, which can be programmable by register settings as shown in the Table 2. DRC_PK_COEF1_ADC DRC_PK_COEF2_ADC... - Page 19 Input (dB) Knee 4 Knee 3 Knee 2 Knee 1 CMP2 Figure 8: DRC Static Characteristic Each section on the characteristic (labeled NG, EXP, CMP2, CMP1, and LMT) can be controlled by setting the slope and knee point values, in their respective registers. The table below provides the corresponding register locations. Static Curve Section Slope Knee Point...

-

Page 20: Limitation

4.1.3 Limitation Due to DC offsets from the ADC block, DRC performance may have limitation. Especially when DRC is designed with 3 or 4 knee points, output level variation caused by DC offsets should be taken into consideration. For DRC design with 2 knee points by setting knee2, knee3, knee4 together, DRC output curves of left and right channels typically share the same track as shown below: Figure 9: DRC Output Curve with 2 Knee Points For DRC with 3 or 4 knee points, systematic DC offsets on both channels will become unnegligible. -

Page 21: Adc Digital Volume Control

4.3 ADC Programmable Biquad Filter The NAU88L21 has 4 dedicated digital biquad filters. Two for the ADC path, and two for the DAC path. The biquad filter is a second-order recursive linear filter with two poles and two zeros. Its transfer function is the Z-domain consists ����... -

Page 22: Companding

Companding is used in digital communication systems to optimize signal-to-noise ratios with reduced data bit rates using non-linear algorithms. The NAU88L21 supports the two main telecommunications companding standards on both transmit and receive sides: A-law and µ-law. The A-law algorithm is primarily used in European communication systems and the µ-law algorithm is primarily used by North America, Japan, and Australia... -

Page 23: Dac Digital Block

5. DAC Digital Block DAC Digital Path Digital Program Volume Program Volume Audio Control Control mable mable ƩΔ Interface Mixer INTP -90~24dB Mixer INTP -90~24dB Biquad Biquad Soft Mute (Sidetone) Soft Mute (Sidetone) Filter Filter Auto Mute Auto Mute Figure 12: DAC Digital Path The DAC digital block uses 24-bit signal processing to generate analog audio with a 16-bit digital sample stream input. -

Page 24: Static Curve

5.1.2 Static Curve The DRC static curve supports five programmable sections, and slope and knee points can be configured as shown in the Table 7. Static Curve Slope Knee Point Section 0, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1 CMP1 0, 1/2, 1/4, 1/8, 1/16, 1 0 to -31dB with -1dB step CMP2... -

Page 25: Dac Digital Volume Control, Mute And Channel Selection

5.5 DAC Path Digital Mixer with Side tone The NAU88L21 implements a channel based digital mixer architecture. Each DAC outputs can be selected between the different inputs. The ADC input channels, I2S channels are capable of being mixed into either output of the DAC. - Page 26 REG0X30[7] DAC_ST_SEL0 REG0X30[15:12] ADC0_TO_DAC0_ST -42dB~0dB/3dB & Mute ADC CH 0 ADC CH 1 REG0X34[7:0] DGAINL_DAC -103dB~24dB/.5dB & Mute Ʃ DAC CH L REG0X2F[15:8] DAC1_TO_DAC0_ST -96dB~24dB/.5dB & Mute DAC CH0 DAC CH1 REG0X2F[7:0] Ʃ DAC0_TO_DAC1_ST DAC CH R -96dB~24dB/.5dB & Mute REG0X30[6] DAC_ST_SEL1 REG0X34[15:8]...

-

Page 27: Companding

Companding is used in digital communication systems to optimize signal-to-noise ratios with reduced data bit rates using non-linear algorithms. The NAU88L21 supports the two main telecommunications companding standards on both transmit and receive sides: A-law and μ-law. The A-law algorithm is primarily used in European communication systems and the μ-law algorithm is primarily used by North America, Japan, and Australia. -

Page 28: Clocking And Sample Rates

Clocking and Sample Rates The internal clocks for the NAU88L21 are derived from a common internal clock source. This master system clock can set directly by the MCLK pin input or it can be generated from a Frequency Locked Loop (FLL) using the MCLK_PIN, BCLK or FS as a reference. -

Page 29: I2S/Pcm Clock Generation

Table 10: Register Settings The internal clock frequency MCLK must be running at 256*Fs (Fs = sample rate in Hz) in order to achieve the best performance. The internal clock frequency MCLK can also run at 400*Fs, which may give a slightly lower performance. For example, when targeting 48 kHz sample rate audio, the MCLK must be set to 256*48k = 12.288MHz, 400*48k = 19.2MHz. - Page 30 BCLK_DIV ÷ MCLK BCLK ÷ LRC_DIV Register: I2S_PCM_CTRL2 Figure 15: BCLK and FS Frequency Selection Bits BCLK_DIV Divided by 1 Divided by 2 Divided by 4 Divided by 8 Divided by 16 Divided by 32 Table 11: Register Settings Bits LRC_DIV Divided by 256 Divided by 128...

-

Page 31: Frequency Locked Loop(Fll)

• Set BCLK_DIV = 1/4 • Set LRC_DIV = 1/64 • Example 3: If we want an Fs of 16 kHz and 32 bit data is to be sent to the I2S TDM bus (4 channels) • BCLK = 16000*32*4 = 2.048MHz and MCLK = 16000*256 = 4.096MHz •... - Page 32 . If the ratio is integer, it still can be on for lower noise output but higher power consumption. • When FLL uses free running mode, NAU88L21 needs to be set as a master in I2S_PCM_CTRL2.MS0 REG0X1D[3]=1 •...

-

Page 33: Control Interfaces

The 2-wire bus is a bidirectional serial bus protocol. This protocol defines any device that sends data onto the bus as a transmitter (or master), and any device receiving data as the receiver (or slave). The NAU88L21 can function only as a slave when in the 2-wire interface configuration. -

Page 34: 2-Wire Write Operation

STOP condition. The Device Address of the NAU88L21 is either 0x1B (CSB=0) or 0x54 (CSB=1). If the Device Address matches this value, the NAU88L21 will respond with the expected ACK signaling as it accepts the data being transmitted to it. -

Page 35: 2-Wire Read Operation

If the device address matches this value, the NAU88L21 will respond with the expected ACK signaling as it accepts the Control Register Address being transmitted into it. After this, the master transmits a second START condition, and a second instantiation of the same device address, but now with R/W=1. -

Page 36: Digital Serial Interface Timing

SDIOH Table 13 Digital Serial Interface Timing Parameters 7.6 Software Reset The NAU88L21 and all of its control registers can be reset to “default”, initial conditions by writing any value to REG0X00 using the two-wire interface mode. Feb 28, 2022 Page 36 of 78 Rev 2.8... -

Page 37: Digital Audio Interfaces

8. Digital Audio Interfaces The NAU88L21 can be configured as either the master or the slave, and the Slave mode is the default if this bit is not written. In master mode, NAU88L21 outputs both Frame Sync (FS) and the audio data bit clock (BCLK) and has full control of the data transfer. -

Page 38: Pcma Audio Data

The PCM time slot mode is used to allocate different time slots for ADC and DAC data. This can be useful when multiple NAU88L21 chips or other devices are sharing the same audio bus. This will allow each chip‟s audio to be delayed around each other without interference. -

Page 39: Tdm I2S Audio Data

The PMC time slot mode can be also used to swap channel 0 and channel 1 audio or cause both channels to use the same data. When using the NAU88L21 with other driver chips, the SDO pin can be set to pull up or pull down or high impedance during no transmission. -

Page 40: Tdm Pcmb Audio Data

The PCM offset mode is used to delay the time at which DAC data is clocked. This increases the flexibility of the NAU88L21 to be used in a wide range of system designs. One key application of this feature is to enable multiple NAU88L21 or other devices to share the audio data bus, thus enabling more than four channels of audio. - Page 41 CHANNEL 3 CHANNEL2 CHANNEL 0 CHANNEL 1 BCLK DACIN/ ADCOUT Figure 34: TDM PCM Offset Audio Format Feb 28, 2022 Page 41 of 78 Rev 2.8...

-

Page 42: Digital Audio Interface Timing Diagrams

8.2 Digital Audio Interface Timing Diagrams 8.2.1 Digital Audio Interface Slave Mode Figure 35 provides the timing for Audio Interface Slave Mode. RISE FALL BCLK (Slave) BCKH BCKL (Slave) DACIN ADCOUT Figure 35 Audio Interface Slave Mode Timing Symbol Description unit BCLK Cycle Time in Slave Mode BCLK High Pulse Width in Slave Mode... -

Page 43: Digital Audio Interface Master Mode

8.2.2 Digital Audio Interface Master Mode provides the timinig for Audio Interface Master Mode BCLK (Master) (Master) DACIN ADCOUT Figure 36 Audio Interface Master Mode Timing Symbol Description unit BCLK Cycle Time in Master Mode BCLK Falling Edge to FS Delay Time in Master Mode DACIN to BCLK Rising Edge Setup Time BCLK Rising Edge to DACIN Hold Time BCLK Falling Edge to ADCOUT Delay Time... -

Page 44: Pcm Audio Interface Slave Mode

8.2.3 PCM Audio Interface Slave Mode I2S or PCM Audio Data can be processed using either Slave Mode or Master Mode. The timing diagram for PCM Audio Data in Slave Mode is shown in Figure 37. Figure 37 PCM Audio Interface Slave Mode 8.2.4 PCM Audio Interface Master Mode I2S or PCM Audio Data can be processed using either Master or Slave Mode. -

Page 45: Pcm Time Slot Audio Interface Slave Mode

8.2.5 PCM Time Slot Audio Interface Slave Mode PCM Time Slot Data can be processed using either Slave Mode or Master Mode. The timing diagram for PCM Time Slot Audio Data in Slave Mode is shown in Figure 39. Figure 39 PCM Time Slot Audio Interface Slave Mode Timing 8.2.6 PCM Time Slot Audio Interface Master Mode The timing diagram for PCM Time Slot Audio Data in Master Mode is shown in Figure 40. -

Page 46: Outputs

9.1 Class G Headphone Driver and Charge Pump The NAU88L21 uses Class G speaker drivers powered by a charge pump for the headphones. For typical operation with large and small signals the charge pump provides ±1.8V and ±0.9V, respectively. These output drivers are driven by dedicated left and right DACs and can provide 30mW of power to a 32Ω... -

Page 47: Control And Status Registers

10. Control and Status Registers Function Name Description HARDWA HARDWARE_ Hardware Reset RE_RST RESET (Write any value once to reset all the registers.) PGA Common Mode Lock Enable Control CMLCK_ENB 0 = Enable (DEFAULT) 1 = Disable DAC Clock Inversion In Analog Domain Enable CLK_DAC_IN Control 0 = Disable (DEFAULT) - Page 48 Function Name Description Scaling Divider For ADC Clock From CODEC_SRC 00 = 1 CLK_ADC_SR 01 = 1/2 (DEFAULT) 10 = 1/4 11 = 1/8 Scaling Divider For DAC Clock From CODEC_SRC 00 = 1 CLK_DAC_SR 01 = 1/2 (DEFAULT) 10 = 1/4 11 = 1/8 Scaling Divider For MCLK From SYSCLK_SRC 0000 = 1 (DEFAULT)

- Page 49 Function Name Description 1000 = x9 1001 = x10 1010 = x12 1011 = x16 1100 = x17 1101 = x18 1110 = x20 1111 = x24 FLL Reference CLK Source Select FLL_CLK_RE 00 = MCLK pin (DEFAULT) F_SRC 01 = MCLK pin 10 = BCLK pin FLL_INTEGE FLL 10-bit Integer Input...

- Page 50 Function Name Description FLL 500KHz Cut-off Frequency Enable Control (If 0x8[14]=1, it sets loop filter cutoff frequency at 600Khz. It will give the best FLL performance with the CUTOFF500 highest power consumption.) 0 = Disable 1 = Enable (DEFAULT) FLL 600KHz Cut-off Frequency Enable Control (If 0x8[14]=1, it sets loop filter cutoff frequency at 600Khz.

- Page 51 Function Name Description Jack Detection Logic Control JKDET_LOGI 0 = OR gate (DEFAULT) 1 = AND gate DEFAULT 0x0000 IRQ Pin Logic Select IRQ_PL 0 = Active low (DEFAULT) 1 = Active high IRQ Pin Pull Select IRQ_PS 0 = Pull down (DEFAULT) 1 = Pull up IRQ Pin Pull Enable Control IRQ_PE...

- Page 52 Function Name Description Jack insertion IRQ status 00 = Cleared state JACK_DET_I 01 = Jack insertion detected 10 = A jack insert interrupt was cleared due to a jack ejection 11 = Undefined DEFAULT READ ONLY Write Operation (Write bits[15:0] clear corresponding REG10 [15:0] INT_CLR_KE INT_CLR_ Write 1s to bits that you want to reset to 0, except)

- Page 53 Function Name Description GPIO2OUT GPIO2 Programmable Output GPIO2JD1 Pull Select GPIO2_PS 0 = Pull up (DEFAULT) 1 = Pull down GPIO2JD1 Drive Current Select GPIO2_DS 0 = Low drive current (DEFAULT) 1 = High drive current GPIO2JD1 Pin Pull Enable Control GPIO2_PE 0 = Enable (DEFAULT) 1 = Disable...

- Page 54 Function Name Description DAC Left Channel Source Under TDM Mode (TDM = 1 & PCM_OFFSET_MODE_CTRL = 0) I2S : 000 = From Slot 0 001= From Slot 1 (DEFAULT) 010 = From Slot 2 011 = From Slot 3 100 = RESERVED 101 = RESERVED DAC_LEFT_S 110 = RESERVED...

- Page 55 Function Name Description 10 = 24-bit word length (DEFAULT) 11 = 32-bit word length Audio Interface Data Format Select 00 = Right justified AIFMT0 01 = Left justified 10 = Standard I2S format (DEFAULT) 11 = PCMA or PCMB audio data format option DEFAULT 0x000A I2S Tri State Enable Control...

- Page 56 Function Name Description BIQ0_ DEFAULT 0x0000 COF1 BIQ0_A1_H Program ADC BIQ0_A1 Parameter Bit[18:16] BIQ0_ COF2 DEFAULT 0x0000 BIQ0_A2_L Program ADC BIQ0_A2 Parameter Bit[15:0] BIQ0_ COF3 DEFAULT 0x0000 BIQ0_A2_H Program ADC BIQ0_A2 Parameter Bit[18:16] BIQ0_ COF4 DEFAULT 0x0000 BIQ0_B0_L Program ADC BIQ0_B0 Parameter Bit[15:0] BIQ0_ COF5 DEFAULT...

- Page 57 Function Name Description CIC_GAIN_AD Gain Adjustment (Fine tunes the DAC output) DAC Oversample Rate Select DAC_RATE 000 = 64 001 = 256 010 = 128 (DEFAULT) 100 = 32 DEFAULT 0x0082 RESERVED RESERVED Bit Numbers Of Dithering On SD Modulator (Step size is 1bit.) 0000 = No dithering (DEFAULT) 0001 = 1...

- Page 58 Function Name Description ADC to DAC CH1 Sidetone Select (Step size is 3dB.) 0x00 = Mute (DEFAULT) ADC_TO_DA 0x01 = -42dB C_ST1 ▼ 0x0E = -3dB 0x0F = 0dB DAC CH0 Sidetone Source Select 0 = Select ADC CH0 as the side tone source of the DAC_ST_SEL DAC CH0 (DEFAULT) 1 = Select ADC CH1 as the side tone source of the...

- Page 59 Function Name Description 1 = Enable Left Channel Headphone Driver Manual Mute MUTE_HSPG Enable Control 0 = Disable (DEFAULT) 1 = Enable Left Channel Headphone Driver Volume Control 00 = 0dB (DEFAULT) HSPGA1_VOL 01 = -3dB 10 = -6dB 11 = -9dB Right Channel Headphone Driver Volume Control 00 = 0dB (DEFAULT) HSPGA2_VOL...

- Page 60 Function Name Description DRC ADC Channel Enable Control DRC_ENA_A 0 = Disable (DEFAULT) 1 = Enable DRC ADC Knee Point 2 Select (Step size is 1dB.) 0x00 = 0dB 0x01 = -1dB DRC_KNEE2_ ▼ IP_ADC 0x14 = -20dB (DEFAULT) ▼ 0x3E = -62dB 0x3F = -63dB ADC_DR...

- Page 61 Function Name Description DRC ADC Peak Detection Attack Time (Ts = 1/SMPL_RATE) 0000 = Ts 0001 = 3*Ts DRC_PK_CO 0010 = 7*Ts 0011 = 15*Ts EF1_ADC (DEFAULT) 0100 = 31*Ts 0101 = 63*Ts 0110 = 127*Ts 0111 = 255*Ts 1001= 511*Ts DRC ADC Peak Detection Release Time (Ts = 1/SMPL_RATE) 0000 = 63*Ts...

- Page 62 Function Name Description DRC DAC Knee Point 3 Select (Step size is 1dB.) 0x00 = -18dB 0x01 = -19dB DRC_KNEE3_ ▼ IP_DAC 0x12 = -36dB (DEFAULT) ▼ 0x1E = -80dB 0x1F = -81dB DEFAULT 0x0F12 DRC DAC Noise Gate Slope DRC_NG_SLP 00 = 1:1 01 = 2:1...

- Page 63 Function Name Description DEFAULT 0x0000 BIQ1_A1_H Program DAC BIQ1_A1 Parameter Bit[18:16] BIQ1_ COF2 DEFAULT 0x0000 BIQ1_A2_L Program DAC BIQ1_A2 Parameter Bit[15:0] BIQ1_ COF3 DEFAULT 0x0000 BIQ1_A2_H Program DAC BIQ1_A2 Parameter Bit[18:16] BIQ1_CO DEFAULT 0x0000 BIQ1_B0_L Program DAC BIQ1_B0 Parameter Bit[15:0] BIQ1_ COF5 DEFAULT...

- Page 64 Function Name Description Impedance Measurement Threshold To Avoid False Detection (Each increase raises the floor of the ADC requiring higher signal levels before activation.) IMM_THRESH 0x00 = [23:0] Full Range (DEFAULT) 0x01 = [23:1] ▼ 0x14 = [23:20] 0x15 = [23:21] Signal Level Of The 23Hz Sinewave Generation For Impedance Measurement IMM_GEN_VO...

- Page 65 Function Name Description OTPDOUT_H OTP Read Out Data High 2 Bits OTPDOU DEFAULT READ ONLY Ram Test Enable Control RAM_TEST_S 0 = Disable (DEFAULT) TART 1 = Enable MISC_CT ADC To DAC Loop 0 = Disable (DEFAULT) D2A_LOOP 1 = Enable (use ADC decimation filter output as DAC Left filter input) DEFAULT 0x0000...

- Page 66 Function Name Description DAC Test Signal TESTDACIN 00 & 11 = GND (DEFAULT) 01 & 10 = High & Low GPIO2JD1 Pull Up Select PULLUP_ 0 = 1MOhm (DEFAULT) GPIO2 1 = 100KOhm GPIO2 JKDET1 Threshold Low Select 00 = 0.22 x VDDA (DEFAULT) GPIO2THL 10 = 0.40 x VDDA 11 = 0.5 x VDDA...

- Page 67 Function Name Description DEFAULT 0x0000 RESERVED RESERVED ANALOG MIC Detection Power Down Control PDMICDET 0 = Power on MIC detection (DEFAULT) _ADC_1 1 = Power down MIC detection DEFAULT 0x0011 RESERVED RESERVED Left Channel PGA Bias Current Increase Enable Control ADC_UPL (For driving ADC at high sample rates) 0 = Disable (DEFAULT)

- Page 68 Function Name Description MICBIAS1 Internal 2K Ohm Resistor For MCGND Enable Control INT2KA 0 = Disable (DEFAULT) 1 = Enable Low Power / Low Noise Mode Select LOWNOISE 0 = Low power mode (DEFAULT) 1 = Low noise mode MICBIAS1 Power Enable Control POWERUP 0 = Disable (DEFAULT) 1 = Enable...

- Page 69 Function Name Description Adjust HS Boost P-driver Bias Current PAMP_THRS 00 = Normal (DEFAULT) 11 = Decrease current Adjust HS Boost N-driver Bias Current NAMP_THRS 00 = Normal (DEFAULT) 11 = Decrease current DEFAULT 0x0000 Charge Input To VREF Enable Control (Effective when DISCHRG = 1) 0 = Disable (DEFAULT) ACDC_CTRL...

- Page 70 Function Name Description Output Driver Power Enable Control (To reduce pop noise, turn on this first, then turn on PUP_MAIN_DRV) PUP_DRV_IN 0 = Disable (DEFAULT) 1 = Enable Bit0 = Left HP driver Bit1 = Right HP driver Main Driver Power Enable Control 0 = Disable (DEFAULT) PUP_MAIN_D 1 = Enable...

- Page 71 Function Name Description Monitor Charge Pump Drawing DC Current NODCBUF 0 = Drawing 1 = Not drawing (DEFAULT) Monitor Charge Pump Enable Status RN2BUF 0 = Off (DEFAULT) 1 = On Monitor High Voltage Status Of VPOS VPOSOK 0 = Possible short circuit (DEFAULT) 1 = Max output (Normal operation) Monitor Low Voltage &...

-

Page 72: Typical Application Diagram

11. Typical Application Diagram VDDA VDDMIC 200 Ω OMTP MICDET MICBIAS BCLK VDDMIC MCLK VREF VDDA QFN 32-pin *200R *2kΩ 10kΩ VSSA Ω VSSD VDDB *10u VDDA CPOUTP SCLK VSSCP SDIO 10nF 10nF Zobel Zobel VDDB Network Network Note: * indicates optional components for improved noise reduction (refer to section 3.5) Feb 28, 2022 Page 72 of 78 Rev 2.8... - Page 73 Package Information 32-lead plastic QFN 32L; 5X5mm2, 0.8mm thickness, 0.5mm lead pitch (Saw Type) EP SIZE 3.5X3.5 mm Feb 28, 2022 Page 73 of 78 Rev 2.8...

- Page 74 Feb 28, 2022 Page 74 of 78 Rev 2.8...

- Page 75 32-lead plastic QFN 32L; 4X4mm2, 0.8mm(Max) thickness, 0.4mm lead pitch (Saw Type) EP SIZE 3.5X3.5 mm Feb 28, 2022 Page 75 of 78 Rev 2.8...

- Page 76 Part Number Dimension Package Package Material NAU88L21YG 5x5 mm QFN-32 Green NAU88L21IG 4x4 mm QFN-32 Green NAU88L21 _ _ Package Material: Pb-free Package Package Type: 32-Pin QFN Package 32-Pin QFN Package Feb 28, 2022 Page 76 of 78 Rev 2.8...

- Page 77 13. Revision History Version ESCRIPTION Date Page(s) February 18, 2019 initial version March 8, 2019 Front page Add Cap-free and internal Resistor in MICBIAS June, 12, 2019 Add Zebol Network in Application circuit. September, 22, 2019 Added RC for MICDET – noise coupling. October, 17, 2019 Modified Figure 42:2-Wire Read Sequence.

- Page 78 All Insecure Usage shall be made at customer’s risk, and in the event that third parties lay claims to Nuvoton as a result of customer’s Insecure Usage, customer shall indemnify the damages and liabilities thus incurred by Nuvoton.

Need help?

Do you have a question about the NAU88L21 and is the answer not in the manual?

Questions and answers