Subscribe to Our Youtube Channel

Summary of Contents for Arbor Technology EmETX-a55E0

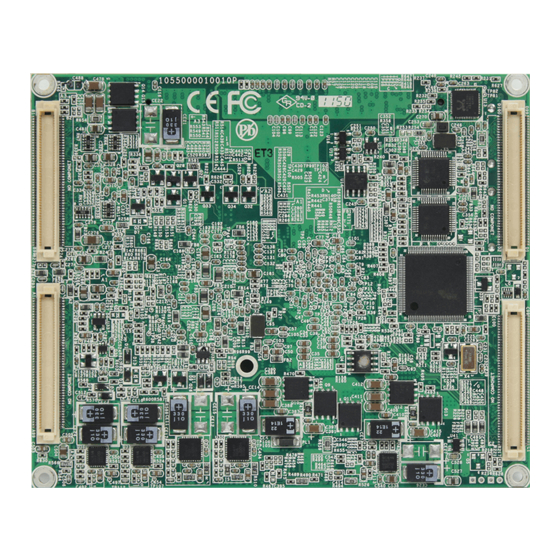

- Page 1 EmETX-a55E0 ® AMD Fusion G-series ETX CPU Module User’s Manual Version 1.0 2012.06...

- Page 2 This page is intentionally left blank.

-

Page 3: Table Of Contents

Table of Contents Chapter 1 - Introduction ............1 1.1 Copyright Notice ............2 1.2 Declaration of Conformity ........2 1.3 About This User’s Manual ........4 1.4 Warning ..............4 1.5 Replacing the Lithium Battery .........4 1.6 Technical Support .............4 1.7 Warranty ..............5 1.8 Packing List ...............6 1.9 Ordering Information ..........6 1.10 Specifications ............7 1.11 Board Dimensions...........8... - Page 4 3.6 Save & Exit...............54 3.7 AMI BIOS Checkpoints ...........56 3.7.1 Checkpoint Ranges ...........56 3.7.2 Standard Checkpoints ........57 Appendix .................65 Appendix A: I/O Port Address Map ......66 Appendix B: BIOS Memory Map ........69 Appendix C: Interrupt Request Lines (IRQ) ....70 Appendix D: Watchdog Timer (WDT) Setting .....72 - ii -...

-

Page 5: Chapter 1 Introduction

Introduction Chapter 1 Introduction Chapter 1 - Introduction - 1 -... -

Page 6: Copyright Notice

Introduction 1.1 Copyright Notice All Rights Reserved. The information in this document is subject to change without prior notice in order to improve the reliability, design and function. It does not represent a commitment on the part of the manufacturer. Under no circumstances will the manufacturer be liable for any direct, indirect, special, incidental, or consequential damages arising from the use or inability to use the product or documentation, even if advised of the possibility of such... - Page 7 RoHS ARBOR Technology Corp. certifies that all components in its products are in compliance and conform to the European Union’s Restriction of Use of Haz- ardous Substances in Electrical and Electronic Equipment (RoHS) Directive 2002/95/EC.

-

Page 8: About This User's Manual

Introduction 1.3 About This User’s Manual This user’s manual provides general information and installation instructions about the product. This User’s Manual is intended for experienced users and integrators with hardware knowledge of personal computers. If you are not sure about any description in this booklet. please consult your vendor before further handling. -

Page 9: Warranty

Introduction 1.7 Warranty This product is warranted to be in good working order for a period of two years from the date of purchase. Should this product fail to be in good working order at any time during this period, we will, at our option, replace or repair it at no additional charge except as set forth in the following terms. -

Page 10: Packing List

1 x Quick Installation Guide If any of the above items is damaged or missing, contact your vendor immediately. 1.9 Ordering Information EmETX-a55E0-T56N AMD G-T56N Dual Core ETX CPU Module HS-55E0-F1 Heat spreader HS-55E0-C1 CPU module cooler for 18W APU (114*95*29.5mm) PBE-1000 R2.1... -

Page 11: Specifications

Introduction 1.10 Specifications Form Factor ETX® CPU Module Soldered onboard AMD G-Fusion T-56N 1.65GHz Processor Chipset AMD FCH A55E 1 x 204-pin DDR3 SO-DIMM Socket up to 4GB System Memory 1333MHz SDRAM Integrated Radeon HD 6320 with Analog RGB/ VGA/ LCD Controller 24-bit dual channels LVDS (Dual independent displays) Ethernet... -

Page 12: Board Dimensions

Introduction 1.11 Board Dimensions 29.5 Unit: mm - 8 -... -

Page 13: Chapter 2 Installation

Installation Chapter 2 Installation Chapter 2 - Installation - 9 -... -

Page 14: Connectors

Installation 2.1 Connectors SATA1, SATA2 Connectors Description LPC1 Connector Connector type: FPC12-14P-P0.5 (Hirose) Description Description LAD0 BUF_PLT_RST# LAD1 LAD2 PCLK_CONN LAD3 LFRAME# +3.3V INT_SERIRQ +3.3V DDI1 Connector Connector type: FH12-26S-0.5SH (Hirose) Description Description DDI_TX0+ DDI_AUX+ DDI_TX0- DDI_AUX- DDI_TX1+ DDI_HPD DDI_TX1- SMB_DAT SMB_CLK DDI_TX2+... - Page 15 Installation ETX1 Connector ETX2 Connector A1 GND GND A2 B1 GND GND B2 A3 PCICLK3 PCICLK4 A4 B3 SD14 SD15 B4 A5 GND GND A6 B5 SD13 MASTER# B6 A7 PCICLK1 PCICLK2 A8 B7 SD12 DREQ7 B8 A9 REQ#3 GNT#3 A10 B9 SD11 DACK#7 B10 A11 GNT#2...

- Page 16 Installation ETX3 Connector ETX4 Connector C1 GND GND C2 D1 GND GND D2 C3 R B C4 D3 5V_SB PWGIN D4 C5 HSY G C6 D5 PS_ON SPEAKER D6 C7 VSY Analog RGB_DDC_CLK C8 D7 PWERBTN# BATT D8 C9 DETECT# Analog RGB_DDC_ATA C10 D9 KBINH LILED D10...

-

Page 17: Block Diagram

Installation 2.2 Block Diagram Single Channel DDR3 DDI connector 1 x SO-DIMM socket 1333MHz FH12-26S-0.5SH Realtek 10/100 1xPCIex1 RTL8105E AMD APU Mbps LAN controller G-series Chrontel PATA Host G-T56N 1xPCIex1 DDI0 (as eDP) Dual Chnnels Primary CH7511 Controller 24-bit LVDS eDP to LVDS IDE ATA I/F JMB368... -

Page 18: Driver Installation Paths

Installation 2.3 Driver Installation Paths Windows 2000 & XP Driver Path \EmETX-a55E0\GRAPHICS\XP\8.92-111109a- CHIPSET & VGA 129010C-EDG_Direct \EmETX-a55E0\ETHERNET\WinXP\PCIE_ Install_5792_01142012 AUDIO \EmETX-a55E0\AUDIO\WinXP\WDM_R267 Windows 7 Driver Path \EmETX-a55E0\GRAPHICS\Win7\8.92-111109a- CHIPSET & VGA 129011C-EDG_Direct \EmETX-a55E0\ETHERNET\win7\Install_ Win7_7050_01162012 AUDIO \EmETX-a55E0\AUDIO\Win7\Vista_Win7_R267 - 14 -... -

Page 19: Chapter 3 - Bios

BIOS Chapter 3 BIOS Chapter 3 - BIOS - 15 -... -

Page 20: Bios Main Setup

BIOS 3.1 BIOS Main Setup The AMI BIOS provides a setup utility program for specifying the system configurations and settings which are stored in the BIOS ROM of the system. When you turn on the computer, the AMI BIOS is immediately activated. After you have entered the setup utility, use the left/right arrow keys to highlight a particular configuration screen from the top menu bar or use the down arrow key to access and configure the information below. - Page 21 BIOS System Date Set the system date. Note that the ‘Day’ automatically changes when you set the date. The date format is: Day : Sun to Sat Month : 1 to 12 Date : 1 to 31 Year : 1998 to 2099 System Time Set the system time.

-

Page 22: Advanced Settings

BIOS 3.2 Advanced Settings Legacy OpROM Support Launch PXE OpROM Enable or disable the boot option for legacy network devices. Launch Storage OpROM Enable or Disable Boot Option for Legacy Mass Storage Devices with Option ROM. Launch Video OpROM Execution of the Legacy Option ROM for video devices. The choice: Enabled (Default), Disabled, Enabled when no UEFI driver - 18 -... -

Page 23: Pci Subsystem Settings

BIOS 3.2.1 PCI Subsystem Settings PCI ROM Priority In case of multiple Option ROMs (Legacy and EFI Compatible), specifies what PCI Option ROM to launch. PCI Latency Timer Value to be programmed into PCI Latency Timer Register. VGA Palette Snoop Enables or Disables VGA Palette Registers Snooping. - Page 24 BIOS PCI Express Settings Relaxed Ordering Enables or Disables PCI Express Device Relaxed ordering. Extended Tag If Enabled, allows Device to use 8-bit Tag field as a requester. No Snoop Enables or Disables PCI Express Device No Snoop Option. Maximum Payload Set Maximum Payload of PCI Express Device or allow System BIOS to select the value.

- Page 25 BIOS Maximum Read Request Set Maximum Read Request of PCI Express Device or allow System BIOS to select the value. The choice: Auto, 128 bytes, 256 bytes, 512 bytes, 1024 bytes, 2048 bytes, 4096 bytes ASPM Support Set the ASPM Level: - Force L0s: Force all links to L0s State - AUTO: BIOS auto configure: - DISABLE: Disables ASPM.

-

Page 26: Acpi Settings

BIOS 3.2.2 ACPI Settings AC Power Shutdown mode Choose AC Power Shutdown mode. The choice: AT Mode, ATX Mode - 22 -... -

Page 27: Cpu Configuration

BIOS 3.2.3 CPU Configuration The CPU Configuration setup screen varies depending on the installed processor. Limit CPUID Maximum Disabled for Windows XP. PSS Support Enable/Disable the generation of ACPI _PPC, _PPS, and _PCT objects. PSATATE Adjustment Provide to adjust startup P-state level. The choice: PState 0, PState 1, PState 2 PPC Adjustment Provide to adjust _PPC object. - Page 28 BIOS SVM Mode Enable/Disable CPU Virtualization. C6 Mode Enable/Disable C6. CPB Mode Auto/disable CPB. Node 0 Information - 24 -...

-

Page 29: Ide Configuration

BIOS 3.2.4 IDE Configuration - 25 -... -

Page 30: Usb Configuration

BIOS 3.2.5 USB Configuration Legacy USB Support Enable Legacy USB support. AUTO option disables legacy support if no USB devices are connected. DISABLE option will keep USB devices avail- able only for EFI applications. The choice: Enabled (Default); Auto; Disabled EHCI Hand-off Allow you to enable support for operating systems without an EHCI hand-off feature. -

Page 31: W83977 Second Super Io Configuration

BIOS Device power-up delay — Maximum time the device will take before it prop- erly reports itself to the host controller. ‘Auto’ uses default value: for a Root port it is 100ms, for a Hub port the delay is taken from hub descriptor. The choice: Auto (Default);... - Page 32 BIOS Serial Port 0 Configuration - 28 -...

- Page 33 BIOS Serial Port 1 Configuration - 29 -...

-

Page 34: F71869 Super Io Configuration

BIOS 3.2.7 F71869 Super IO Configuration Restore AC Power Loss Select Restore AC Power Loss mode. The choice: Last State, Always On, Bypass Mode, Always Off - 30 -... - Page 35 BIOS Serial/Parallel Port 0/1 Configuration Serial Port Use the Serial port option to enable or disable the serial port. The choice: Enabled, Disabled Change Settings Use the Change Settings option to change the serial port’s IO port address and interrupt address. The choice: Auto IO=3F8h;...

-

Page 36: F71869 H/W Monitor

BIOS 3.2.8 F71869 H/W Monitor - 32 -... -

Page 37: Wake Event

BIOS 3.2.9 Wake Event Wake On Lan Enable/Disable Wake On Lan help. - 33 -... -

Page 38: Chipset

BIOS 3.3 Chipset This section allows you to configure and improve your system; also, set up some system features according to your preference. - 34 -... -

Page 39: North Bridge

BIOS 3.3.1 North Bridge - 35 -... - Page 40 BIOS GFX Configuration Primary Video Device Select Primary Video Device that BIOS will use for output. NB GPP Core Config Configure NB GPP Core. The choice: Disabled, GPP_CORE_x4x4, GPP_CORE_x4x2x2, GPP_ CORE_x4x2x1x1, GPP_CORE_x4x1x1x1x1 LVDS Output Enable/Disable NB PCIe Connect Type (Display type). Display port output Enable/Disable NB PCIe Connect Type (Display type).

- Page 41 BIOS Memory Configuration Integrated Graphics The Integrated Graphics controller configuration is set to Auto. The choice: Disabled, Force, Auto Bank Interleaving The choice: Disabled, Enabled IOMMU Mode IOMMU is supported on LINUX based systems to convert 32bit I/O to 64bit MMIO.

- Page 42 BIOS Node 0 Information - 38 -...

-

Page 43: South Bridge

BIOS 3.3.2 South Bridge - 39 -... - Page 44 BIOS SB SATA Configuration OnChip SATA Channel Enable/Disable Serial ATA. OnChip SATA Type The choice: Native IDE, RAID, AHCI, Legacy IDE, IDE→AHCI, AHCI as ID 0x4394, IDE→AHCI as ID 0x4394 OnChip IDE mode OnChip IDE mode Select. The choice: Legacy mode, Native mode SATA IDE Combined Mode Enable/Disable SATA IDE Combined Mode.

- Page 45 BIOS SATA Power on PORT0/1 Enable/Disable SATA Power on PORT0/1. The choice: Enabled, Power Down SB USB Configuration USB PORT 0~3 Enable/Disable USB PORT 0~13/FL0~1. USB Device Wakeup From S3 or S4 Enable/Disable USB Device Wakeup From S3 or S4. - 41 -...

- Page 46 BIOS SB GEC Configuration In-Chip NIC Enable/Disable In-Chip NIC. GEC Resume Wake from S5 Enable/Disable GEC Resume Wake from S5. GEC OPROM Enable/Disable GEC OPROM. - 42 -...

- Page 47 BIOS SB GPP Port Configuration SB GPP Function Enable/Disable SB GPP Function. GPP Port Link Configuration Select GPP Port Link Configuration. Hide Unused GPP Ports Enable/Disable Hide Unused GPP Ports. NB-SB PHY PLL Power Down Enable/Disable NB-SB PHY PLL Power Down. SB GPP PHY PLL Power Down Enable/Disable SB GPP PHY PLL Power Down.

- Page 48 BIOS SB HD Azalia Configuration HD Audio Azalia Device The choice: Auto, Disabled, Enabled HD Onboard PIN Config The choice: Disabled, Enabled Azalia Front Panel The choice: Auto, Disabled SDIN0~3 PIN Config The choice: GPIO, Azalia Azalia Snoop The choice: Disabled, Enabled - 44 -...

- Page 49 BIOS EC Configuration - 45 -...

- Page 50 BIOS SB IMC Fan Configuration IMC Fan Control The choice: Disabled, Enabled Zone 0~3 Support The choice: Disabled, Enabled - 46 -...

- Page 51 BIOS Zone 0 Config Zone 0 Fan Out The choice: No Fan, FANOUT 0~4 Zone 0 Fan Speed Mode The choice: Linear Mode, Step Mode Fan Frequency Set fan frequency. Zone 0 Temperature Sensor The choice: No Sensor, TEMPIN 0~3, Int TEMP, SB-TSI or ADT7461ARMZ, ADM1032 or ADT7461ARM Zone 0 Temperature Average The choice: Disabled, Enabled...

-

Page 52: Boot Settings

BIOS 3.4 Boot Settings The Boot menu items allow you to change the system boot options. Boot Configuration Setup Prompt Timeout Seconds to wait for setup activation key. 65535(0xFFFF) means indefinite waiting. Bootup NumLock State This setting determines whether the Num Lock key should be activated at boot up. - Page 53 BIOS Option ROM Messages This item is to set display mode for Option ROM. Interrupt 19 Capture When enabled, it allows the optional ROM to trap interrupt 19. CSM Support Enabled/ disabled CSM support. If Auto is selected, based on OS, CSM will be enabled/ disabled automatically.

-

Page 54: Security

BIOS 3.5 Security Administrator Password Use this feature to set the Administrator Password which is required to enter the BIOS setup utility. The length of the password should be from 3-characters to 8-characters long. User Password Use this feature to set a User Password which is required to log into the system and to enter the BIOS setup utility. - Page 55 BIOS Secure Boot Policy Internal FV/ Option ROM/ Removable Media/ Fixed Media Image Execution Policy on Security Violation. Image load device path. The choice: Always Execute, Always Execute, Allow Execute, Defer Execute, Deny Execute, Query User - 51 -...

- Page 56 BIOS Key Management Set PK from File Launches the Filebrowser to set the Platform Key from file. Get PK to File Stores the existing Platform Key to file name OK in selected file system’s root. Delete the PK Deletes the Platform Key. Set KEK to File Launches the Filebrowser to set the Key Exchange Key Signature Database from file.

- Page 57 BIOS Append an entry to KEK Launches the Filebrowser to Append the Key Exchange Key Signature Data- base entry from file. Set DB from File Launches the Filebrowser to set the Authorized Signature Database from file. Get DB to File Stores the existing Authorized Signature Database to file name DB in selected file system’s root.

-

Page 58: Save & Exit

BIOS 3.6 Save & Exit Save Changes and Exit Pressing <Enter> on this item and it asks for confirmation: Save configuration changes and exit setup? Pressing <OK> stores the selection made in the menus in CMOS - a special section of memory that stays on after you turn your system off. The next time you boot your computer, the BIOS configures your system according to the Setup selections stored in CMOS. - Page 59 BIOS Discard Changes and Reset Reset system setup without saving any changes. Save Changes Save changes done so far to any of the setup options. Discard Changes Discard changes done so far to any of the setup options. Restore Defaults Restore system to factory default.

-

Page 60: Ami Bios Checkpoints

BIOS 3.7 AMI BIOS Checkpoints 3.7.1 Checkpoint Ranges Status Code Range Description 0x01 – 0x0B SEC execution 0x0C – 0x0F SEC errors PEI execution up to and including memory 0x10 – 0x2F detection 0x30 – 0x4F PEI execution after memory detection 0x50 –... -

Page 61: Standard Checkpoints

BIOS 3.7.2 Standard Checkpoints SEC Phase Status Code Description 0x00 Not used Progress Codes 0x01 Power on. Reset type detection (soft/hard). 0x02 AP initialization before microcode loading 0x03 North Bridge initialization before microcode loading 0x04 South Bridge initialization before microcode loading 0x05 OEM initialization before microcode loading 0x06... - Page 62 BIOS PEI Phase Status Code Description Progress Codes 0x10 PEI Core is started 0x11 Pre-memory CPU initialization is started 0x12 Pre-memory CPU initialization (CPU module specific) 0x13 Pre-memory CPU initialization (CPU module specific) 0x14 Pre-memory CPU initialization (CPU module specific) 0x15 Pre-memory North Bridge initialization is started Pre-Memory North Bridge initialization (North Bridge...

- Page 63 BIOS 0x32 CPU post-memory initialization is started 0x33 CPU post-memory initialization. Cache initialization CPU post-memory initialization. Application Processor(s) 0x34 (AP) initialization CPU post-memory initialization. Boot Strap Processor 0x35 (BSP) selection CPU post-memory initialization. System Management 0x36 Mode (SMM) initialization 0x37 Post-Memory North Bridge initialization is started Post-Memory North Bridge initialization (North Bridge 0x38...

- Page 64 BIOS 0x55 Memory not installed 0x56 Invalid CPU type or Speed 0x57 CPU mismatch 0x58 CPU self test failed or possible CPU cache error CPU micro-code is not found or micro-code update is 0x59 failed 0x5A Internal CPU error 0x5B reset PPI is not available 0x5C-0x5F Reserved for future AMI error codes...

- Page 65 BIOS 0xF9 Recovery capsule is not found 0xFA Invalid recovery capsule 0xFB – 0xFF Reserved for future AMI error codes DXE Phase Status Code Description 0x60 DXE Core is started 0x61 NVRAM initialization 0x62 Installation of the South Bridge Runtime Services 0x63 CPU DXE initialization is started 0x64...

- Page 66 BIOS South Bridge DXE Initialization (South Bridge module 0x74 specific) South Bridge DXE Initialization (South Bridge module 0x75 specific) South Bridge DXE Initialization (South Bridge module 0x76 specific) South Bridge DXE Initialization (South Bridge module 0x77 specific) 0x78 ACPI module initialization 0x79 CSM initialization 0x7A –...

- Page 67 BIOS 0xA4 SCSI initialization is started 0xA5 SCSI Reset 0xA6 SCSI Detect 0xA7 SCSI Enable 0xA8 Setup Verifying Password 0xA9 Start of Setup 0xAA Reserved for ASL (see ASL Status Codes section below) 0xAB Setup Input Wait 0xAC Reserved for ASL (see ASL Status Codes section below) 0xAD Ready To Boot event 0xAE...

- Page 68 BIOS 0xD7 No Console Input Devices are found 0xD8 Invalid password 0xD9 Error loading Boot Option (LoadImage returned error) 0xDA Boot Option is failed (StartImage returned error) 0xDB Flash update is failed 0xDC Reset protocol is not available ACPI/ASL Checkpoints Status Code Description 0x01...

-

Page 69: Appendix

Appendix Appendix Appendix - 65 -... -

Page 70: Appendix A: I/O Port Address Map

Appendix Appendix A: I/O Port Address Map Each peripheral device in the system is assigned a set of I/O port addresses which also becomes the identity of the device. The following table lists the I/O port addresses used. Address Device Description 0x00000000-0x000003AF PCI bus 0x00000000-0x000003AF... - Page 71 Appendix 0x0000F100-0x0000F10F Standard Dual Channel PCI IDE Controller 0x000001F0-0x000001F7 Primary IDE Channel 0x000003F6-0x000003F6 Primary IDE Channel 0x00000170-0x00000177 Secondary IDE Channel 0x00000376-0x00000376 Secondary IDE Channel 0x00000A79-0x00000A79 ISAPNP Read Data Port 0x00000279-0x00000279 ISAPNP Read Data Port 0x00000274-0x00000277 ISAPNP Read Data Port 0x0000040B-0x0000040B Motherboard resources 0x000004D6-0x000004D6 Motherboard resources...

- Page 72 Appendix 0x00000064-0x00000064 Standard 101/102-Key or Microsoft Natural PS/2 Keyboard 0x000003F8-0x000003FF Communications Port (COM1) 0x000002F8-0x000002FF Communications Port (COM2) 0x00000378-0x0000037F Printer Port (LPT1) 0x00000020-0x00000021 Programmable interrupt controller 0x000000A0-0x000000A1 Programmable interrupt controller 0x00000081-0x00000083 Direct memory access controller 0x00000087-0x00000087 Direct memory access controller 0x00000089-0x0000008B Direct memory access controller 0x0000008F-0x0000008F Direct memory access controller...

-

Page 73: Appendix B: Bios Memory Map

Appendix Appendix B: BIOS Memory Map Address Device Description 0xA0000-0xBFFFF PCI bus 0xA0000-0xBFFFF VgaSave 0xC0000-0xDFFFF PCI bus 0x80000000-0xFFFFFFFF PCI bus 0x68000000-0x7FFFFFFF Motherboard resources 0xC0000000-0xCFFFFFFF Video Controller (VGA Compatible) 0xFEB00000-0xFEB3FFFF Video Controller (VGA Compatible) 0xFEB44000-0xFEB47FFF Microsoft UAA Bus Driver for High Definition Audio 0xFEA00000-0xFEAFFFFF PCI standard PCI-to-PCI bridge... -

Page 74: Appendix C: Interrupt Request Lines (Irq)

Appendix 0xFED00000-0xFED00FFF High precision event timer 0xFFC00000-0xFFFFFFFF Motherboard resources 0xFEB4A000-0xFEB4AFFF Standard OpenHCD USB Host Controller 0xFEB49000-0xFEB49FFF Standard OpenHCD USB Host Controller 0xFEB48000-0xFEB480FF Standard Enhanced PCI to USB Host Con- troller 0xE0000000-0xEFFFFFFF System board FED45000-FED8FFFF Motherboard resources FED90000-FED93FFF Motherboard resources FEE00000-FEEFFFFF Motherboard resources FF000000-FFFFFFFF Intel(R) 82802 Firmware Hub Device... - Page 75 Appendix IRQ 18 Standard OpenHCD USB Host Controller IRQ 18 Standard OpenHCD USB Host Controller IRQ 18 Standard OpenHCD USB Host Controller IRQ 10 Ethernet Controller IRQ 7 Communications Port (COM3) IRQ 7 Communications Port (COM4) IRQ 1 Standard 101/102-Key or Microsoft Natural PS/2 Keyboard IRQ 12 Microsoft PS/2 Mouse IRQ 4...

-

Page 76: Appendix D: Watchdog Timer (Wdt) Setting

Appendix Appendix D: Watchdog Timer (WDT) Setting WDT is widely used for industry application to monitor the activity of CPU. Application software depends on its requirement to trigger WDT with adequate timer setting. Before WDT time out, the functional normal system will reload the WDT. - Page 77 Appendix This page is intentionally left blank. - 73 -...

Need help?

Do you have a question about the EmETX-a55E0 and is the answer not in the manual?

Questions and answers