Table of Contents

Advertisement

Quick Links

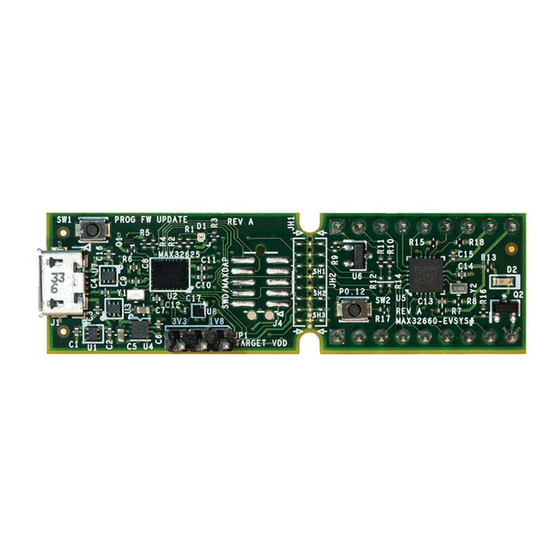

MAX32660 USER GUIDE

UG6659; Rev 0; 7/18

Abstract:

This user guide provides application developers information on how to use the memory and

peripherals of the MAX32660 microcontroller. Detailed information for all registers and fields in the

device are covered. Guidance is given for managing the clocks, power and initialization of the product.

Maxim Integrated

Page 1 of 195

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for Maxim Integrated MAX32660

- Page 1 This user guide provides application developers information on how to use the memory and peripherals of the MAX32660 microcontroller. Detailed information for all registers and fields in the device are covered. Guidance is given for managing the clocks, power and initialization of the product.

- Page 2 MAX32660 User Guide Table of Contents Introduction ..............................13 Overview ..............................13 Memory, Register Mapping, and Access ..................... 15 System Clocks, Reset, and Power Management ..................21 Maxim Integrated Page 2 of 195...

- Page 3 MAX32660 User Guide Flash Controller ............................51 General-Purpose I/O and Alternate Function Pins ..................58 DMA Controller ............................71 Maxim Integrated Page 3 of 195...

- Page 4 MAX32660 User Guide UART ................................84 Real-Time Clock (RTC) ..........................96 Timers ..............................105 Maxim Integrated Page 4 of 195...

- Page 5 MAX32660 User Guide Watchdog Timer (WDT) ........................126 C Master/Slave Serial Controller ......................131 Maxim Integrated Page 5 of 195...

- Page 6 MAX32660 User Guide Serial Peripheral Interface 0 (SPI0) ...................... 159 SPIMSS (SPI1/I S) ..........................178 Maxim Integrated Page 6 of 195...

- Page 7 MAX32660 User Guide Trademarks ............................195 Revision History ............................ 195 Maxim Integrated Page 7 of 195...

-

Page 8: Table Of Contents

MAX32660 User Guide List of Figures Figure 2-1: MAX32660 High Level Block Diagram ....................14 Figure 3-1: Code Memory Mapping ........................15 Figure 3-2: Data Memory Map ..........................16 Figure 4-1: Clock Tree Diagram ..........................24 Figure 7-1: DMAC Block Diagram ..........................71 Figure 9-1. - Page 9 MAX32660 User Guide List of Tables Table 3-1: APB Peripheral Base Address Map ......................19 Table 4-1: Operating Voltage Range Selection and the Effect on V and f ............ 21 CORE HFIO Table 4-2: Minimum Flash Wait State Setting for Each OVR Setting (f )..........

- Page 10 MAX32660 User Guide Table 6-2: GPIO Port, Pin Name and Alternate Function Matrix, 20-TQFN ............59 Table 6-3: Standard GPIO Drive Strength Selection ....................61 Table 6-4: GPIO with I C Alternate Function Drive Strength Selection ..............61 Table 6-5: GPIO Mode and Alternate Function Selection ..................61 Table 6-6: GPIO Port Interrupt Vector Mapping .....................

- Page 11 MAX32660 User Guide Table 8-7: UART Interrupt Flags Register ........................ 92 Table 8-8: UART Rate Integer Register ........................93 Table 8-9: UART Baud Rate Decimal Register......................93 Table 8-10: UART FIFO Register ..........................94 Table 8-11: UART DMA Configuration Register ....................... 94 Table 8-12: UART TX FIFO Data Output Register .....................

- Page 12 MAX32660 User Guide Table 13-4. Clock Phase and Polarity Operation ....................164 Table 13-5: SPI0 Master Register Addresses and Descriptions ................169 Table 13-6: SPI FIFO Data Registers ........................169 Table 13-7: SPI Master Signals Control Registers ....................169 Table 13-8: SPI Transmit Packet Size Register ....................... 171 Table 13-9: SPI Static Configuration Registers ......................

-

Page 13: Introduction

MAX32660 User Guide Introduction For ordering information, mechanical and electrical characteristics for the MAX32660 family of devices please refer to the datasheet. For information on the Arm® Cortex®-M4 with FPU core, please refer to the Cortex-M4 with FPU Technical Reference Manual. -

Page 14: Figure 2-1: Max32660 High Level Block Diagram

MAX32660 User Guide Figure 2-1: MAX32660 High Level Block Diagram Maxim Integrated Page 14 of 195... -

Page 15: Memory, Register Mapping, And Access

MAX32660 User Guide Memory, Register Mapping, and Access Overview The Arm Cortex-M4 with FPU core defines a standard memory space for unified code and data access. This memory space is addressed in units of single bytes but is most typically accessed in 32-bit (4 byte) units. It may also be accessed, depending on the implementation, in 8-bit (1 byte) or 16-bit (2 byte) widths. -

Page 16: Figure 3-2: Data Memory Map

Many standard memory regions are defined for the Arm Cortex-M4 architecture; the use of many of these is optional for the system integrator. At a minimum, the MAX32660 must contain code and data memory for application code, stack and heap usage, as well as certain components which are part of the implemented architecture. - Page 17 0x2001 7FFF. The entirety of the SRAM memory space on the MAX32660 is contained within the dedicated Arm Cortex-M4 with P ’s SRAM bit-banding region from 0x2000 0000 to 0x200F FFFF (1MB maximum for bit-banding). This means that the CPU can access the entire SRAM either using standard byte/word/doubleword access or using bit-banding operations.

- Page 18 MAX32660 User Guide On the MAX32660, access to the region that contains most peripheral registers (0x4000 0000 to 0x400F FFFF) goes from the AHB bus through an AHB-to-APB bridge. This allows the peripheral modules to operate on the slower, easier to handle APB bus matrix.

-

Page 19: Table 3-1: Apb Peripheral Base Address Map

MAX32660 User Guide 3.3.5 Core AHB Interface 3.3.5.1 I-Code This AHB master is used by the Arm core for instruction fetching from memory instances located in code space from byte addresses 0x0000 0000 to 0x1FFF FFFF. This bus master is used to fetch instructions from the internal flash memory. - Page 20 MAX32660 User Guide Peripheral Peripheral Base Address End Address Register Prefix I2C0_ 0x4001 D000 0x4001 DFFF I2C1_ 0x4001 E000 0x4001 EFFF Standard DMA DMA_ 0x4002 8000 0x4002 8FFF Flash Controller FLC_ 0x4002 9000 0x4002 93FF Internal Cache Controller ICC_ 0x4002 A000...

-

Page 21: System Clocks, Reset, And Power Management

32.768kHz External Oscillator. The MAX32660 coordinates OVR change between the internal LDO and the HFIO set frequency. When changing the OVR setting, the MAX32660 must be operating from the internal LDO. In a system using an external supply for V , firmware must transition to the internal LDO prior to changing the OVR setting. - Page 22 MAX32660 User Guide The following steps describe how to change the OVR: 1. Ensure the part is operating from the internal LDO for V CORE Set PWRSEQ_LP_CTRL.ldo_dis to 0. b. If using an external supply for V , ensure the external supply is set to the same voltage as the current OVR CORE setting.

-

Page 23: Table 4-2: Minimum Flash Wait State Setting For Each Ovr Setting

MAX32660 User Guide Note: When changing the system clock prescaler to move from a slower system clock frequency to a faster system clock frequency, always set the Flash Wait State field to the minimum required for the faster system clock frequency prior to changing the system oscillator prescaler. -

Page 24: Figure 4-1: Clock Tree Diagram

MAX32660 User Guide System Clocks Figure 4-1, below, shows a high-level diagram of the MAX32660 clock tree. Figure 4-1: Clock Tree Diagram The selected System Oscillator (SYSOSC) is the clock source for most internal blocks. Select SYSOSC from the following clock sources: •... -

Page 25: Table 4-3: Reset Sources And Effect On Oscillator Status

Oscillator settings are not reset during a Soft Reset or Peripheral Reset. Table 4-3 sh ws ach scillat r’s nabl stat f r each type of reset source in the MAX32660. Table 4-4 details the effect each reset source has on the System Clock selection and the System Clock prescaler settings. - Page 26 4.3.1 High-Frequency Internal Oscillator The MAX32660 includes a High-Frequency Internal Oscillator (HFIO) that is the default system oscillator after a POR, System and Watchdog Reset. To enter DEEPSLEEP, the HFIO must be powered down by setting register bit GCR_PM.hfiopd to 1. Failure to set this bit to 1 will inhibit the processor from entering DEEPSLEEP.

- Page 27 For the low power modes, the Arm Cortex-M4 with FPU does not execute code. Each low power mode of operation supports wakeup events that result in the MAX32660 to re-enter ACTIVE mode operation. For SLEEP mode, wakeup events include any external or internal interrupt, RTC wakeup, and the Watchdog Interrupt. DEEPSLEEP and BACKUP mode wakeup events are limited to any enabled GPIO external interrupt or from an enabled RTC wakeup event.

-

Page 28: Table 4-5: Wake-Up Sources For Each Low-Power Mode

Table 4-5, below, lists the wake-up sources for each of the low-power modes supported by the MAX32660. Wake-up from a GPIO interrupt and the RTC alarm must be enabled by the application to wake-up the device from SLEEP, DEEPSLEEP and BACKUP mode. -

Page 29: Table 4-6: Reset And Low Power Mode Effects

On completion of any of the four reset cycles, all peripherals are reset, HCLK and PCLK are operational, the CPU core receives clocks and power, and the device enters ACTIVE mode. Program execution begins at the reset vector address. Each peripheral in the MAX32660 can be reset individually by firmware using the GCR_RST0 GCR_RST1 registers. - Page 30 MAX32660 User Guide Peripheral Soft System ACTIVE SLEEP DEEPSLEEP BACKUP Reset Reset Reset Mode Mode Mode Mode 8kHz Osc High Freq Osc Auto Off PCLK HCLK CPU Clock CORE CPU State Retention Reset Reset Reset Reset Standard DMA Reset Reset...

-

Page 31: Table 4-7: Instruction Cache Controller Register Addresses And Descriptions

MAX32660 User Guide 4.8.3 Flushing the ICC0 Cache The System Configuration Register (GCR_SCON) includes a field for flushing ICC0. Setting GCR_SCON.ccache_flush to 1 performs a flush of ICC0’s 16K ach an th tag . Set the ICC0_INVALIDATE register to 1 to invalidate the ICC0 cache and force a cache flush. -

Page 32: Table 4-10: Icc Cache Control Register

(ICC0), and the peripheral FIFOs. 4.10.1 On-Chip Cache Management The MAX32660 includes an instruction cache controller for code fetches from the flash memory. The cache can be enabled, disabled, and zeroized and the cache clock can be disabled by placing it in Light Sleep. Refer to section Instruction Cache Controller for details. -

Page 33: Table 4-12: Global Control Registers, Offsets And Descriptions

MAX32660 User Guide 4.10.3 RAM Low Power Modes RAM can be placed in a low power mode, referred to as Light Sleep, using register GCR_MEM_CTRL, Memory Clock Control. Light Sleep gates off the clock to the RAM and makes the RAM unavailable for read/write operations. The RAM contents are retained during Light Sleep mode. -

Page 34: Table 4-14: Reset 0 Register

Description System Reset Write 1 to perform a System Reset of the MAX32660. When set to 1, the system reset resets everything on the device except the AoD registers and the RAM retention. All other registers, peripherals, the CPU core and the watchdog timer are reset. This field is cleared... - Page 35 MAX32660 User Guide Reset 0 Register GCR_RST0 [0x0004] Bits Name Access Reset Description Soft Reset Write 1 to perform a soft reset. A soft reset resets all peripherals including the GPIO port pin configuration but does not reset the Watchdog Timer peripheral.

-

Page 36: Table 4-15: System Clock Control Register

MAX32660 User Guide Reset 0 Register GCR_RST0 [0x0004] Bits Name Access Reset Description Timer1 Reset Write 1 to reset the peripheral state to the reset default state. When complete this field will read 0. timer1 R/W1O 0: TMR1 peripheral not in reset. - Page 37 MAX32660 User Guide System Clock Control Register GCR_CLK_CTRL [0x0008] Bits Name Access Reset Description 32.768kHz External Oscillator Ready Status On POR or System Reset this field is set to 0. Setting GCR_CLK_CTRL.x32k_en to 1 forces this field to 0 and hardware sets this field to 1 automatically when the oscillator is ready for use.

-

Page 38: Table 4-16: Power Management Register

RTC Alarm Wakeup Enable When this field is set to 1, If the RTC is configured to generate a wakeup alarm, an RTC wakeup event causes the MAX32660 to exit all low power modes and transition directly to ACTIVE mode. Refer to section 9.2.3 RTC Wakeup From DEEPSLEEP/BACKUP Power... - Page 39 MAX32660 User Guide Peripheral Clocks Disable 0 Register GCR_PCLK_DIS0 [0x0024] Bits Name Access Reset Description I2C1 Clock Disable Setting this field disables the APB clock to this peripheral. When the clock is disabled, the peripheral power consumption is reduced, and the peripheral is disabled. Disabling the cl ck t th p riph ral s n t aff ct th p riph ral’s r gist rs.

-

Page 40: Table 4-18: Memory Clock Control Register

MAX32660 User Guide Peripheral Clocks Disable 0 Register GCR_PCLK_DIS0 [0x0024] Bits Name Access Reset Description UART0 Clock Disable Setting this field disables the APB clock to this peripheral. When the clock is disabled, the peripheral power consumption is reduced, and the peripheral is disabled. Disabling the cl ck t th p riph ral s n t aff ct th p riph ral’s r gist rs. - Page 41 MAX32660 User Guide Memory Clock Control Register GCR_MEM_CTRL [0x0028] Bits Name Access Reset Description ICC0 Cache RAM Light Sleep Enable t this fi l t 1 t nabl Light l p m f r th nt rnal ach ntr ll r’s 16K RAM.

-

Page 42: Table 4-19: Memory Zeroization Control Register

MAX32660 User Guide Memory Clock Control Register GCR_MEM_CTRL [0x0028] Bits Name Access Reset Description System RAM 0 Light Sleep Enable Set this field to 1 to enable Light Sleep for System RAM 0 (0x2000 0000 - 0x2000 3FFF). If light sleep is enabled, the System RAM contents are retained but the Data Memory cannot be read. -

Page 43: Table 4-21: Reset Register 1

MAX32660 User Guide System Status Flag Register GCR_SYS_STAT [0x0040] Bits Name Access Reset Description Arm Cortex-M4 with FPU ICE Lock Status Flag This field is set in the factory and if set to 1 disables JTAG SWD access to the device. -

Page 44: Table 4-23: Event Enable Register

MAX32660 User Guide Table 4-23: Event Enable Register Event Enable Register GCR_EVTEN [0x004C] Bits Name Access Reset Description Reserved for Future Use 31:2 Do not modify this field. RX Event Enabled Set this field to 1 to enable generation of an RXEV event to wake the CPU from a Wait for Event (WFE) sleep state. -

Page 45: Table 4-27: Function Control Register 0

1: Configuration Valid cfg_valid Description Note: If this field reads 0 the device configuration is invalid and a device error has occurred. Please contact Maxim Integrated technical support for additional assistance. Table 4-28: System Initialization Address Error Register System Initialization Status Register... -

Page 46: Table 4-31: Power Sequencer Low Power Control Registers, Offsets, Access And Descriptions

When enabled, if the power supply drops below the power fail reset voltage the entire CORE device goes into a Power-On Reset. Refer to the MAX32660 datasheet for the trigger threshold value and power fail reset voltage. When the power supply monitor is tripped, a Power Fail Warning Interrupt is triggered. 4.15 Power Sequencer Registers The PWRSEQ base peripheral address is 0x4000 6800. -

Page 47: Table 4-32: Low Power Voltage Control Register

MAX32660 User Guide 4.15.1 Power Sequencer Register Details Table 4-32: Low Power Voltage Control Register Low Power Voltage Control Register PWRSEQ_LP_CTRL [0x0000] Bits Name Access Reset Description Reserved for Future Use 31:26 Do not modify this field. Power-On-Reset Monitor Disable... - Page 48 MAX32660 User Guide Low Power Voltage Control Register PWRSEQ_LP_CTRL [0x0000] Bits Name Access Reset Description Reserved for Future Use Do not modify this field. RAM Retention Regulator Enable for BACKUP Mode This field selects the source used to retain the RAM contents during BACKUP mode operation.

-

Page 49: Table 4-33: Low Power Mode Wakeup Flags For Gpio0

MAX32660 User Guide Low Power Voltage Control Register PWRSEQ_LP_CTRL [0x0000] Bits Name Access Reset Description System RAM 0 Data Retention Enable for BACKUP Mode Set this field to 1 to enable Data Retention for System RAM 0, address range of 0x2000 0000 to 0x2000 3FFF. - Page 50 MAX32660 User Guide Low-Power Memory Shutdown Register PWRSEQ_LPMEMSD [0x0040] Bits Name Access Reset Description System RAM 2 (0x2000 7FFF - 0x2000 FFFF) Shut Down Write 1 to shut down power to System RAM 2 memory range. sram2_off 0: System RAM 2 Powered On (Enabled)

-

Page 51: Table 5-1: Internal Flash Memory Organization

• Write Protection Overview The MAX32660 contains 256KB of internal flash memory for storing user application and data. The internal flash memory is programmable via the JTAG debug interface (in-system) or directly with user application code (in-application). The flash is organized as an array of pages. Each page is 8,192 bytes per page. -

Page 52: Table 5-2: Valid Addresses For 32-Bit And 128-Bit Internal Flash Writes

MAX32660 User Guide below. For the 96MHz Relaxation Oscillator as the system clock, the FLC_CLKDIV.clkdiv field should be set to 96 (0x60). If another clock source is set as the system clock, this field must be adjusted to meet the target 1MHz for f... -

Page 53: Table 5-3: Page Boundary Address Range For Page Erase Operations

MAX32660 User Guide 5.3.4 Flash Write Perform the following steps to write to the internal flash memory: 1. If desired, enable Flash Controller interrupts by setting the FLC_INTR.access_fail_ie and FLC_INTR.done_ie bits. 2. Set the write field, FLC_CTRL.width, as described in Flash Write Width. -

Page 54: Table 5-4: Flash Controller Registers, Offsets, Access And Descriptions

MAX32660 User Guide 5.3.6 Mass Erase Mass erase clears the internal flash memory. This operation requires the JTAG debug port to be enabled to perform the operation. If the JTAG debug port is not enabled a mass erase operation cannot be performed. Perform the following steps to mass erase the internal flash: 1. - Page 55 MAX32660 User Guide Flash Controller Clock Divisor Register FLC_CLKDIV [0x04] Bits Name Access Reset Description Flash Controller Clock Divisor The system clock is divided by the value in this field to generate the FLC peripheral clock, f . The FLC peripheral clock must equal 1MHz. The default on all forms of...

-

Page 56: Table 5-5: Flash Controller Interrupt Register

MAX32660 User Guide Flash Controller Control Register FLC_CTRL [0x08] Bits Name Access Reset Description Reserved for Future Use Do not modify this field. Page Erase Write a 1 to this field to initiate a page erase at the address in FLC_ADDR.addr. The flash must be unlocked prior to attempting a page erase, see FLC_CTRL.unlock for... -

Page 57: Table 5-6: Flash Controller Data Register 0

MAX32660 User Guide Flash Controller Interrupt Register FLC_INTR [0x24] Bits Name Access Reset Description Flash Access Fail Interrupt Flag This bit is set when an attempt is made to write to the flash while the flash is busy or locked. Only hardware can set this bit to 1. Writing a 1 to this bit has no effect. This bit... - Page 58 General Description The MAX32660 provides up to 14 GPIO pins in the 20-TQFN package and up to 10 GPIO pins in the 16-WLP. Each GPIO pin maps to a GPIO port. For the MAX32660 all GPIO pins are grouped in GPIO port 0 (GPIO0).

-

Page 59: Table 6-1: Gpio Port, Pin Name And Alternate Function Matrix, 16-Wlp

SWD JTAG pins always default to Alternate Function 1 enabled and the SWD JTAG is enabled. This alternate function signal is mappable to more than one GPIO pin but there is only one instance of this peripheral in the MAX32660. - Page 60 Refer to the GPIO Drive Strength for configuration details and the modes supported. b. Reference the MAX32660 datasheet for the electrical characteristics for the drive strength modes. 3. Set the output high or low using the GPIO0_OUT[pin] bit. 6.2.4 GPIO Drive Strength Each I/O pin supports multiple selections for drive strength.

-

Page 61: Table 6-3: Standard Gpio Drive Strength Selection

Drive Strength Drive Strength GPIO_DS0_SEL[pin] = 1.62V = 3.63V 10mA 20mA Note: The drive strength currents shown are targets only. Refer to the MAX32660 Data Sheet Electrical Characteristics table for details of the V and V parameters. OL_GPIO OH_GPIO OL_I2C... -

Page 62: Table 6-6: Gpio Port Interrupt Vector Mapping

MAX32660 User Guide enabled for any number of GPIO on each GPIO port. The following procedure details the steps for enabling Active mode interrupt events for a GPIO pin: 1. Disable interrupts by setting the GPIO0_INT_EN[pin] field to 0. This will prevent any new interrupts on the pin from triggering but will not clear previously triggered (pending) interrupts. -

Page 63: Table 6-8: Gpio Port 0 Registers

MAX32660 User Guide Enable low power mode wakeup (SLEEP, DEEPSLEEP and BACKUP) from an external GPIO event by completing the following steps: 1. Set the polarity (rising or falling edge) by writing to the GPIO0_INT_POL[pin] field. The wakeup functionality uses rising and falling edge detection circuitry that operates asynchronously and does not require an active clock. -

Page 64: Table 6-10: Gpio Output Enable Register

MAX32660 User Guide GPIO Alternate Function 0 Select Register GPIO0_AF0_SEL [0x0000] Bits Name Access Reset Description GPIO Alternate Function 0 Mode Select If JTAG debug is available on the part, this pin defaults to the JTAG alternate function (TCK/SWCLK) on all forms of reset. -

Page 65: Table 6-12: Gpio Input Register

MAX32660 User Guide Table 6-12: GPIO Input Register GPIO Input Register GPIO0_IN [0x0024] Bits Name Access Reset Description Reserved for Future Use 31:14 Do not modify this field. GPIO Input Level Read the state of the corresponding input pin. The input state is always readable for a pin r gar l ss f th pin’s c nfigurati n as an utput r alt rnat functi n. -

Page 66: Table 6-16: Gpio Interrupt Flag Register

MAX32660 User Guide GPIO Interrupt Enable Register GPIO0_INT_EN [0x0034] Bits Name Access Reset Description GPIO Interrupt Enable Enable or Disable the interrupt for the corresponding GPIO pin. 0: GPIO interrupt disabled. 13:0 1: GPIO interrupt enabled. Note: Disabling a GPIO interrupt does not clear pending interrupts for the associated pin. -

Page 67: Table 6-19: Gpio Pullup/Pulldown Enable Register

MAX32660 User Guide Table 6-19: GPIO Pullup/Pulldown Enable Register GPIO Pullup Pulldown Selection 0 Register GPIO0_PULL_EN [0x0060] Bits Name Access Reset Description Reserved for Future Use 31:14 Do not modify this field. GPIO Pull Up/Pull Down Enable Setting this bit to 1 enables either the weak pull-up or weak pull-down resistor on the 13:10 respective pin. -

Page 68: Table 6-23: Gpio Drive Strength 0 Select Register

I/O pin. 0: Fast slew rate selected. 13:10 1: Slow slew rate selected. Note: Refer to the MAX32660 datasheet for detailed electrical characteristics of the fast and slow slew rates. Reserved for Future Use Do not modify this field. -

Page 69: Table 6-24: Gpio Drive Strength 1 Select Register

0: Low output drive strength selected. 1: High output drive strength selected. Refer to V and V in the MAX32660 Data Sheet Electrical Characteristics table OL_I2C OH_I2C for details of the drive strengths for these I/O pins. GPIO Drive Strength 0 Select The output drive strength supports four modes. -

Page 70: Table 6-25: Gpio Pullup/Pulldown Select Register

0: Pull-down resistor selected 13:10 1: Pull-up resistor selected Refer to the MAX32660 Data Sheet Electrical Characteristics table for details of the pull-up/pull-down resistors for the respective I/O pins. Pulldown Resistor Select This bit should always be set to 0. The I/O pins with I C as an alternate function only a weak pull-down resistor. -

Page 71: Figure 7-1: Dmac Block Diagram

MAX32660 User Guide DMA Controller The Direct Memory Access controller (DMAC) is a hardware feature that moves data blocks from peripheral to memory, memory to peripheral, and memory to memory. This data movement reduces the processor load significantly. Figure 7-1 provides a high-level overview of the major DMA Controller components. -

Page 72: Table 7-2: Channel Reload Registers

MAX32660 User Guide In addition, each channel has a set of reload registers, shown in Table 7-2, that are used to chain DMA buffers when a count-to-zero (CTZ) condition occurs. Table 7-2: Channel Reload Registers Register Description DMAn_DST_RLD Destination reload register... -

Page 73: Table 7-3: Source And Destination Address Definition

MAX32660 User Guide DMA Source and Destination Addressing For memory addresses, the DMAn_SRC DMAn_DST registers are used to program the addresses of the source and destination. For peripherals, however, the address is fixed based on the DMAn_CFG.reqsel value set. Table 7-3 shows how the source address, destination address and the address increment controls are constructed based on the DMAn_CFG.reqsel bit. -

Page 74: Table 7-5: Data Movement From The Dma Fifo To Destination

MAX32660 User Guide Register/Bit Field Description Comments This determines the maximum data width used during each read of the AHB DMAn_CFG.srcwd Source width burst (byte, two bytes, or four bytes). The actual AHB width might be less if DMAn_CNT is not great enough to supply all of the needed bytes. - Page 75 MAX32660 User Guide To configure a channel for buffer chaining, initialize the following registers: • DMAn_CFG • DMAn_SRC • DMAn_DST • DMAn_CNT • DMAn_SRC_RLD • DMAn_DST_RLD • DMAn_CNT_RLD When the DMAn_CNT_RLD register is written, the DMAn_CNT_RLD.rlden bit must not be set. In addition, any writes to the DMAn_CFG register prior to initialization must not set the DMAn_CFG.chen and DMAn_CFG.rlden bits.

- Page 76 MAX32660 User Guide When running in normal mode without buffer chaining (DMAn_CFG.rlden = 0), set the DMAn_CFG.chdien bit only. An interrupt is generated upon DMA completion or an error condition (bus error or time-out error). When running in buffer chaining mode (DMAn_CFG.rlden = 1), set both the DMAn_CFG.chdien and DMAn_CFG.ctzien bits.

-

Page 77: Table 7-6: Standard Dma Control Registers, Offsets, Access And Descriptions

MAX32660 User Guide 7.11 Channel and Register Access Restrictions Writing to any register while a channel is disabled is supported, but there are certain restrictions when a channel is enabled. The DMAn_STAT.ch_st bit indicates whether the channel is enabled or not. -

Page 78: Table 7-9: Standard Dma Channel 0 To Channel 15 Offsets

MAX32660 User Guide DMA Interrupt Flag Register DMA_INT_FL [0x0004] Bits Name Access Reset Description ipend Channel Interrupt Each bit in this field represents an interrupt for the corresponding channel. To clear an interrupt, clear the corresponding active interrupt bit in the DMAn_STAT register. -

Page 79: Table 7-11: Dma Configuration Register

MAX32660 User Guide 7.15.1 Standard DMA Channel Configuration Register Details Table 7-11: DMA Configuration Register DMA Configuration Register DMAn_CFG [0x0100] Bits Name Access Reset Description ctzien CTZ Interrupt Enable When enabled, the DMA_INT_FL.ipend bit is set to 1 whenever a CTZ event occurs. - Page 80 MAX32660 User Guide DMA Configuration Register DMAn_CFG [0x0100] Bits Name Access Reset Description 17:16 srcwd Source Width Indicates the width of each AHB transaction from the source peripheral or memory. The actual width might be less than this if the...

-

Page 81: Table 7-12: Dma Status Register

MAX32660 User Guide Table 7-12: DMA Status Register DMA Status Register DMAn_STAT [0x0104] Bits Name Access Reset Description 31:7 Reserved for Future Use Do not modify this field. to_st R/W1C Time-Out Status A time-out occurred if this field reads 1. Write 1 to clear. -

Page 82: Table 7-13: Dma Source Register

MAX32660 User Guide Table 7-13: DMA Source Register DMA Source Register DMAn_SRC [0x0108] Bits Name Access Reset Description 31:0 Source Device Address For peripheral transfers, the actual address field is either ignored or forced to zero because peripherals only have one location to read/write data based on the request select chosen. -

Page 83: Table 7-16: Dma Source Reload Register

MAX32660 User Guide Table 7-16: DMA Source Reload Register DMA Source Reload Register DMAn_SRC_RLD [0x0114] Bits Name Access Reset Description Reserved for Future Use Do not modify this field. 30:0 src_rld Source Address Reload Value If DMAn_CFG.rlden = 1, then the value of this register is loaded into... - Page 84 MAX32660 User Guide UART The MAX32660 microcontroller provides up to two industry-standard UART ports which can communicate with external devices using standard serial communications protocols. The UARTs are full-duplex Universal Asynchronous Receiver/Transmitter (UART) serial ports. Both UARTs, UART0 and UART1, support identical functionality and registers unless specifically noted otherwise.

- Page 85 MAX32660 User Guide UART Interrupts Interrupts can be generated for the following conditions: • The Transmit FIFO level is equal or less than the set transmit threshold. • The Receive FIFO level is equal or greater than the set receieve threshold.

-

Page 86: Table 8-1: Example Baud Rate Calculation Results, Target Bit Rate = 1.8Mbps, F

MAX32660 User Guide Table 8-1: Example Baud Rate Calculation Results, Target Bit Rate = 1.8Mbps, f =48MHz PCLK UARTn_BAUD0 Clock Divider clkdiv 3.256 1.628 0.814 0.407 0.203 Table 8-1, above, shows the DIV result for each of the UARTn_BAUD0.clkdiv field settings. With the Clock Divider set to 8 or 16, the resulting DIV value is greater than 1. -

Page 87: Table 8-2: Uart Registers, Offset Addresses And Descriptions

MAX32660 User Guide Flushing the UART FIFOs The FIFOs can be flushed independently by setting UARTn_CTRL0.rxflush to 1 for the RX FIFO and UARTn_CTRL0.txflush. to 1 for the TX FIFO. The TX FIFO and RX FIFO are automatically flushed if the UART is disabled by clearing the UARTn_CTRL0.enable field (UARTn_CTRL0.enable = 0). - Page 88 MAX32660 User Guide UART Control 0 Register UARTn_CTRL0 [0x0000] Bits Name Access Reset Description RX Timeout Frame Count Set this field to the number of frames before a Receive Timeout occurs. If the RX FIFO contains data, a RX Timeout condition occurs if the time for the number of frames in this register passes without the FIFO receiving any new data.

-

Page 89: Table 8-4: Uart Control 1 Register

MAX32660 User Guide UART Control 0 Register UARTn_CTRL0 [0x0000] Bits Name Access Reset Description Receive FIFO Flush Write 1 to flush the receive FIFO rxflush R/W1O Cleared to 0 by hardware when flush is completed Transmit FIFO Flush Write 1 to flush the Transmit FIFO... -

Page 90: Table 8-5: Uart Status Register

MAX32660 User Guide Table 8-5: UART Status Register UART Status Register UARTn_STAT [0x0008] Bits Name Access Reset Description Reserved for Future Use 31:25 Do not modify this field. RX Timeout This field is set to 1 when a receive timeout occurs. This field is set by hardware when... -

Page 91: Table 8-6: Uart Interrupt Enable Register

MAX32660 User Guide UART Status Register UARTn_STAT [0x0008] Bits Name Access Reset Description TX Busy This field reads 1 when the UART is transmitting data. tx_busy 0: UART is not actively transmitting data. 1: UART is transmitting data. Table 8-6: UART Interrupt Enable Register... -

Page 92: Table 8-7: Uart Interrupt Flags Register

MAX32660 User Guide UART Interrupt Enable Register UARTn_INT_EN [0x000C] Bits Name Access Reset Description RX Parity Error Interrupt Enable Enables an interrupt when a receive parity error is detected. rx_parity_error 0: Interrupt disabled. 1: Interrupt enabled. RX Frame Error Interrupt Enable Enables an interrupt when a receive frame error is detected. -

Page 93: Table 8-8: Uart Rate Integer Register

MAX32660 User Guide UART Interrupt Flags Register UARTn_INT_FL [0x0010] Bits Name Access Reset Description RX FIFO Overrun Interrupt Flag This field is set if the receive FIFO is full and an additional byte is received resulting in a FIFO overrun condition. If this field is set at least one byte of received data has... -

Page 94: Table 8-10: Uart Fifo Register

MAX32660 User Guide UART Baud Rate Decimal Register UARTn_BAUD1 [0x0018] Bits Name Access Reset Description Decimal Portion of Baud Rate Divisor This field contains the remainder portion of the bit rate divisor. Refer to the UART Bit 11:0 dbaud Rate Calculation... - Page 95 MAX32660 User Guide UART TX FIFO Data Output Register UARTn_TXFIFO [0x0024] Bits Name Access Reset Description TX FIFO Data Output Peek Register Reads from this register return the next character available for transmission at the end data of the TX FIFO. If no data is available, 0x00 is returned.

- Page 96 RTC system interrupts. The RTC time base is created using a 32.768kHz crystal connected between the 32KIN and 32KOUT pins on the MAX32660. See the MAX32660 datasheet for detailed connection and pin information related to the 32KIN and 32KOUT pins.

-

Page 97: Figure 9-1. Rtc Block Diagram

MAX32660 User Guide Figure 9-1. RTC Block Diagram RTC Alarm Functions The RTC provides time-of–day and sub-second interval alarm functions. The time-of-day alarm is implemented by matching the count values in the counter register with the value stored in the alarm register. The sub-second interval alarm provides an auto-reload timer that is driven by the trimmed RTC clock source. - Page 98 9.2.3 RTC Wakeup From DEEPSLEEP/BACKUP Power Modes The RTC alarms are an optional wakeup source for the MAX32660 during DEEPSLEEP/BACKUP mode. Perform the following steps to use the RTC as a DEEPSLEEP/BACKUP wakeup source: 1. Configure the RTC Time-of-Day Alarm for the required number of seconds.

- Page 99 MAX32660 User Guide 9.3.1 RTC Register Write Protection The RTC_CTRL.busy bit is a read-only status bit controlled by hardware and set when any of the following conditions occur: • System Reset. • Software writes to the RTC_SEC register or RTC trim registers.

-

Page 100: Table 9-1. Rtc Registers, Offsets And Descriptions

The RTC is capable of outputting the raw 4KHz signal or a trim compensated 1KHz or 512Hz signal to the 32KCAL alternate pin function. On both the 16 WLP package and the 20 TQFN package for the MAX32660 the 32KCAL is alternate function 2 on pin P0.2. -

Page 101: Table 9-3: Rtc Sub-Seconds Counter Register

MAX32660 User Guide Table 9-3: RTC Sub-Seconds Counter Register RTC Sub-Seconds Counter Register RTC_SSEC [0x04] Bits Name Access Reset Description 31:8 Reserved for Future Use Do not modify this field. rtss Sub-Seconds Counter This field represents sub-seconds and increments at 256Hz. When this field rolls from 0xFF to 0x00, the RTC_SEC.count increments. - Page 102 MAX32660 User Guide RTC Control Register RTC_CTRL [0x10] Bits Name Access Reset Description 12:11 x32k_mode 32kHz Oscillator Mode Select Selects the operating mode for the 32kHz oscillator. 0: Operates in noise immunity mode 1: Operates in quiet mode. Oscillator warm-up is not required.

-

Page 103: Table 9-7: Rtc Trim Register

MAX32660 User Guide RTC Control Register RTC_CTRL [0x10] Bits Name Access Reset Description alarm_ss_en Sub-Second Alarm Interrupt Enable Set this bit to 1 to enable the RTC sub-second alarm interrupt. Check the RTC_CTRL.busy flag after writing this bit to determine when the RTC synchronization is complete. - Page 104 MAX32660 User Guide RTC Oscillator Control Register RTC_OSCCTRL [0x18] Bits Name Access Reset Description bypass RTC Crystal Bypass Bypass the crystal oscillator to allow a digital square wave to be driven on the 32KIN pin. 0: Disable bypass (POR default) 1: Enable bypass Note: This field is only reset on POR and not effected by other forms of reset.

- Page 105 MAX32660 User Guide Timers The MAX32660 contains three 32-bit, reloadable timers. Each timer provides multiple operating modes. Timer modes supported include: • One-Shot: Timer counts up to terminal value then halts. • Continuous: Timer counts up to terminal value then repeats.

- Page 106 Timer Pin Functionality On the MAX32660, only Timer 0 supports a Timer Pin. The timer pin functionality is mapped as an alternate function that is shared with a GPIO. Timer pin assignments are detailed in the data sheet for the specific device.

-

Page 107: Figure 10-1: One-Shot Mode Diagram

MAX32660 User Guide 10.4 One-Shot Mode (000b) In One-shot mode the timer peripheral increments TMRn_CNT until it matches TMRn_CMP and then stops incrementing and disables the timer. The timer can optionally output a pulse on the timer pin at the end of the timer period. In this mode, the timer must be re-enabled to start another one-shot mode event. - Page 108 MAX32660 User Guide 10.4.2 Configuration Configure the timer for One-Shot mode by doing the following: 1. Set TMRn_CN.ten = 0 to disable the timer 2. Set TMRn_CN.tmode to 000b to select One-shot mode. 3. Set TMRn_CN.pres3:TMRn_CN.pres to set the prescaler that determines the timer frequency.

-

Page 109: Figure 10-2: Continuous Mode Diagram

MAX32660 User Guide 10.5 Continuous Mode (001b) In Continuous mode, the timer peripheral increments TMRn_CNT until it matches TMRn_CMP, resets TMRn_CNT 0x0000 0001, and continues incrementing. The timer peripheral can optionally toggle the state of the timer pin at the end of the timer period. - Page 110 MAX32660 User Guide 10.5.2 Configuration Configure the timer for Continuous mode by performing the following steps: 1. Set TMRn_CN.ten = 0 to disable the timer. 2. Set TMRn_CN.tmode to 001b to select Continuous mode. 3. Set TMRn_CN.pres3:TMRn_CN.pres to set the prescaler that determines the timer frequency.

-

Page 111: Figure 10-3: Counter Mode Diagram

MAX32660 User Guide 10.6 Counter Mode (010b) In Counter mode, the timer peripheral increments TMRn_CNT when a transition occurs on the timer pin. When TMRn_CNT = TMR.CMP, the interrupt bit is set, TMRn_CNT is set to 0x0000 0001, and continues incrementing. The timer can be configured to increment on either the rising edge or the falling edge, but not both. - Page 112 MAX32660 User Guide 10.6.2 Configuration Configure the timer for Counter mode by doing the following: 1. Set TMRn_CN.ten = 0 to disable the timer. 2. Set TMRn_CN.tmode to 010b to select Counter mode. 3. Configure the timer pin: Configure the pin as a timer input and configure the electrical characteristics as needed.

- Page 113 MAX32660 User Guide 10.7 PWM Mode (011b) In PWM mode, the timer sends a Pulse-Width Modulated (PWM) output using th tim r’s utput signal. The timer first counts up to the match value stored in the TMRn_PWM register. At the end of the cycle where the...

- Page 114 MAX32660 User Guide If TMRn_CN.tpol is 0, the ratio of the PWM output high time to the total period is calculated using the following equation: ( ������_������ – ������_������ ) ������ ������������ ℎ����ℎ �������� ���������� ( % ) = × 100 ������_������...

-

Page 115: Figure 10-4: Capture Mode Diagram

MAX32660 User Guide 10.8 Capture Mode (100b) Capture mode most often used to measure the time between events. The timer increments from an initial value until an g transiti n ccurs n th tim r pin. his trigg rs th ‘captur ’ v nt which c pi s TMRn_CNT to the TMRn_PWM.pwm... - Page 116 MAX32660 User Guide The timer period event occurs on the timer clock TMRn_CNT = TMRn_CMP. The timer peripheral automatically performs the following actions when an end of timer period event occurs: 1. The value in TMRn_CNT is reset to 0x0000 00001. The timer remains enabled and continues incrementing.

-

Page 117: Figure 10-5: Counter Mode Diagram

MAX32660 User Guide 10.9 Compare Mode (101b) In Compare mode the timer peripheral increments continually, allowing the timer to be a programmable 32-bit programmable period timer. The end of timer period event occurs when the timer value matches the compare value, but the timer continues to increment until the count reaches 0xFFFF FFFF. - Page 118 MAX32660 User Guide 10.9.2 Configuration Configure the timer for Compare mode by doing the following: 1. Set TMRn_CN.ten = 0 to disable the timer. 2. Set TMRn_CN.tmode to 011b to select Compare mode. 3. Set TMRn_CN.pres3:TMRn_CN.pres to set the prescaler that determines the timer frequency.

-

Page 119: Figure 10-6: Gated Mode Diagram

MAX32660 User Guide 10.10 Gated Mode (110b) Gated mode is like continuous mode, except that TMRn_CNT only increments when the timer pin is in its active state. Figure 10-6: Gated Mode Diagram TMR_CN.TPL = 0 TIMER PIN (INPUT) TMR_CN.TPL = 1 TIMER CLOCK TMR_CN.TEN... - Page 120 MAX32660 User Guide 10.10.2 Configuration Configure the timer for Gated mode by doing the following: 1. Set TMRn_CN.ten = 0 to disable the timer. 2. Set TMRn_CN.tmode to 110b to select Gated mode. 3. Set TMRn_CN.pres3:TMRn_CN.pres to set the prescaler that determines the timer frequency.

- Page 121 MAX32660 User Guide 10.11 Capture/Compare Mode (111b) In Capture/Compare mode, the timer starts counting after the first external timer input transition occurs. The transition, a rising edge or falling edge on the tim r’s input signal, is set using the TMRn_CN.tpol bit.

-

Page 122: Table 10-1: Timer Register Offsets, Names, Access And Descriptions

Timer Count Register for Timer 0 is TMR0_CNT while the Timer Count Register for Timer 1 is TMR1_CNT, and so on. The MAX32660 includes three timer instances, TMR0, TMR1 and TMR2. The base address for TMR0, TMR1 and TMR2 are as follows: •... -

Page 123: Table 10-4: Timer Pwm Registers

MAX32660 User Guide Table 10-4: Timer PWM Registers Timer PWM Register TMRn_PWM [0x0008] Bits Name Access Reset Description 31:0 Timer PWM Match or Timer Capture Value PWM Mode: In PWM mode, this field sets the count value for the first transition period of the PWM cycle. - Page 124 MAX32660 User Guide Timer Control Register TMRn_CN [0x0010] Bits Name Access Reset Description tpol Timer Polarity Selects the p larity f th tim r’s input an utput signal. his s tting is n t us th GP P rt Pin f r th tim r’s input, utput, r b th is n t c nfigur f r th tim r alternate function in GPIO.

- Page 125 MAX32660 User Guide Timer Control Register TMRn_CN [0x0010] Bits Name Access Reset Description tmode Timer Mode Select ts th tim r’s p rating m tmode Selected Timer Mode 000b One-Shot 001b Continuous 010b Counter 011b 100b Capture 101b Compare 110b...

-

Page 126: Figure 11-1: Watchdog Timer Block Diagram

MAX32660 User Guide Watchdog Timer (WDT) The watchdog timer protects against corrupt or unreliable software, power faults, and other system-level problems, which may place the microcontroller into an improper operating state. When the application is executing properly, application software periodically resets the watchdog counter. If the watchdog timer interrupt is enabled and the software does not reset the counter within the interrupt time period (WDT0_CTRL.int_period), the watchdog timer generates a watchdog... -

Page 127: Table 11-1: Watchdog Timer Interrupt Period With F

MAX32660 User Guide 11.2 Usage Utilizing the watchdog timer in the application software is straightforward. As early as possible in the application software, enable the watchdog timer interrupt and watchdog timer reset. Periodically the application software must write to the WDT0_RST register to reset the watchdog counter. - Page 128 MAX32660 User Guide WDT0_CTRL INT_PERIOD int_period (seconds) 0.280 0.560 1.12 2.24 4.47 8.95 17.9 Disabled 11.4 Enabling the Watchdog Timer The watchdog timers are free running and require a protected sequence of writes to enable the watchdog timers to prevent an unintended reset during the enable process.

-

Page 129: Table 11-2: Watchdog Timer Registers

MAX32660 User Guide 11.8 Watchdog Timer Registers The WDT0 base peripheral address is 0x4000 3000. Refer to Table 3-1: APB Peripheral Base Address Map for the addresses of all APB mapped peripherals. Table 11-2: Watchdog Timer Registers Address Register Name... -

Page 130: Table 11-4: Watchdog Timer Reset Register

MAX32660 User Guide Watchdog Timer 0 Control Register WDT0_CTRL 0x0000 [0x00] Bits Name Access Reset Description Reset Period Sets the number of PCLK cycles until a system reset occurs if the watchdog timer is not reset. 0xF: 2 × ��... -

Page 131: Table 12-1: I 2 C Bus Terminology

MAX32660 User Guide C Master/Slave Serial Controller The MAX32660 integrates two I C peripherals, designated I2C0 and I2C1. The register interfaces for I2C0 and I2C1 are identical with the same offset addresses for each register. For simplicity, I2Cn is used throughout this section to refer to both I C ports (where n = [0,1]). -

Page 132: Figure 12-1: The Roles Of I C Devices And The Direction The I C Signals

MAX32660 User Guide For all of the above roles, the Master is responsible for initiating the transfer and generating the clock signal on the SCL line. Figure 12-1, below, shows the four roles and the direction of the communication on the SCL and SDA lines. - Page 133 R/W bit. The I C peripheral in the MAX32660 supports both 7-bit and 10-bit addressing. However, some slave addresses are reserved for special purposes by the I C specification, including, but not limited to the following: •...

-

Page 134: Figure 12-2: I C Write Data Transfer

MAX32660 User Guide • Address 0b0000 x is reserved by the I C specification for special purposes and should not be used for a slave address. • Address 0b1111 1 x is reserved by the I C specification for special purposes and should not be used for a slave address. - Page 135 12.3.8 SCL and SDA Bus Drivers The I C bus expects SCL and SDA to be open-drain signals. In the MAX32660, once the I C peripheral is enabled and the proper GPIO alternate function is selected, the corresponding pad circuits are automatically configured as open-drain outputs.

-

Page 136: Figure 12-3: I C Specification Minimum And Maximum Clock Parameters For Standard And Fast Mode

MAX32660 User Guide 12.3.10 SCL Clock Configurations The SCL frequency is dependent upon the values of I C peripheral clock and the values of the external resistor and capacitor on the SCL clock line. Note: An external RC load on the SCL line will affect the target SCL frequency calculation. - Page 137 MAX32660 User Guide The I C controller can hold SCL low in both master and slave modes after an ACK bit transmission. w v r, th t rm ‘cl ck str tching’ as in th C Bus Specification only applies if performed by a slave device. When an I C master holds the SCL line low, the master is technically varying the clock speed.

-

Page 138: Table 12-2: I C Address Byte Format

MAX32660 User Guide For applications where an external device may hold the SCL line low longer than the maximum timeout supported, the timeout can be disabled by setting the timeout field to 0 (I2Cn_TIMEOUT.to = 0). 12.6 C Addressing After a START or RESTART condition, an address byte is transmitted where the first seven bits are the address, and the last bit indicates to the slave if the operation is a read or a write. - Page 139 MAX32660 User Guide 12.7 C TX FIFO and RX FIFO Management There are separate transmit and receive FIFOs, TX FIFO and RX FIFO. Both are accessed using the FIFO Data register I2Cn_FIFO. Writes to this register enqueue data into the TX FIFO. Writes to a full TX FIFO have no effect. Reads from I2Cn_FIFO dequeue data from the RX FIFO.

- Page 140 MAX32660 User Guide While I C peripheral is waiting for the application firmware to clear the I2Cn_INTFL0.irxmi flag, firmware can disable Interactive Receive Mode and, if operating as a master, load the remaining number of bytes to be received for the transaction.

- Page 141 MAX32660 User Guide Note for receive operations, the length of the DMA transaction (in bytes) must be an integer multiple of I2Cn_RXCTRL0.rxth. Otherwise, the receive transaction will end with some data still in the RX FIFO, but not enough to trigger an interrupt to the DMA, leaving the DMA transaction incomplete.

-

Page 142: Figure 12-4: I C Clock Period

MAX32660 User Guide Note that this arbitration scheme works with any number of bus masters: if more than two masters begin transmitting simultaneously, the arbitration continues as each master cedes the bus until only one master remains transmitting. Data is not corrupted because as soon as each master realizes it has lost arbitration it stops transmitting, leaving the data on SDA intact. - Page 143 MAX32660 User Guide Because the controller does not start counting the high/low time until the input buffer detects the new value, the actual clock behavior is based on many factors. These include bus loading, other devices on the bus holding SCL low, and the filter delay time of this device.

-

Page 144: Table 12-3: I C Registers

MAX32660 User Guide The required steps for implementing TX FIFO Preloading in an application are as follow: 1. Set I2Cn_TXCTRL1.txrdy to 0 2. Enable TX FIFO Preloading by setting I2Cn_TXCTRL1.txpreld to 1. 3. If the TX FIFO Lockout Flag (I2Cn_INTFL0.txloi) is set to 1, write 1 to clear the flag and enable writes to the TX FIFO. -

Page 145: Table 12-4: I 2 C Control Registers 0

MAX32660 User Guide Offset Register Name Access Description [0x0034] I2Cn_CLKLO C Clock Low Time Register [0x0038] I2Cn_CLKHI C Clock High Time Register [0x003C] I2Cn_HS_CLK C Hs-Mode Clock Control Register [0x0040] I2Cn_TIMEOUT C Timeout Register [0x0044] I2Cn_SLADDR C Slave Address Register... - Page 146 MAX32660 User Guide C Control 0 Register I2Cn_CTRL0 [0x0000] Bits Name Access Reset Description SCL Status Returns the current logic level of the SCL hardware pin. 0: SCL pin is logic low. 1: SCL pin is logic high. SDA Pin Control Set the state of the SDA hardware pin (actively pull low or float).

-

Page 147: Table 12-5: I C Status Registers

MAX32660 User Guide Table 12-5: I C Status Registers C Status Register I2Cn_STATUS [0x0004] Bits Name Access Reset Description Reserved for Future Use 31:12 Do not modify this field. C Controller Status This field indicates the status of the I C controller. -

Page 148: Table 12-6: I 2 C Interrupt Status Flags Registers 0

MAX32660 User Guide C Status Register I2Cn_STATUS [0x0004] Bits Name Access Reset Description Bus Busy If set, the I C bus is active. busy 0: Bus is idle 1: Bus is busy Table 12-6: I C Interrupt Status Flags Registers 0... - Page 149 MAX32660 User Guide C Interrupt Status Flags 0 Register I2Cn_INTFL0 [0x0008] Bits Name Access Reset Description Master Mode Arbitration Lost Interrupt Flag Write 1 to clear. Write 0 has no effect. arberi R/ W1C 0: Condition has not occurred. 1: Condition occurred.

-

Page 150: Table 12-7: I C Interrupt Enable 0 Registers

MAX32660 User Guide Table 12-7: I C Interrupt Enable 0 Registers C Interrupt Enable 0 Register I2Cn_INTEN0 [0x000C] Bits Name Access Reset Description Reserved for Future Use 31:16 Do not modify this field. TX FIFO Locked Out Interrupt Enable Set this field to enable events for TX FIFO lock events. -

Page 151: Table 12-8: I C Interrupt Status Flags 1 Registers

MAX32660 User Guide C Interrupt Enable 0 Register I2Cn_INTEN0 [0x000C] Bits Name Access Reset Description RX FIFO Threshold Level Interrupt Enable Set this field to enable interrupt events when an RX FIFO threshold event occurs. rxthie 0: Interrupt disabled. 1: Interrupt enabled. -

Page 152: Table 12-10: I C Fifo Length Registers

MAX32660 User Guide C Interrupt Enable 1 Register I2Cn_INTEN1 [0x0014] Bits Name Access Reset Description Slave Mode RX FIFO Overflow Interrupt Enable In slave mode operation, set this field to enable the RX FIFO overflow interrupt. rxofie 0: Interrupt disabled. -

Page 153: Table 12-12: I C Receive Control 1 Registers

MAX32660 User Guide Table 12-12: I C Receive Control 1 Registers C Receive Control 1 Register I2Cn_RXCTRL1 [0x0020] Bits Name Access Reset Description Reserved for Future Use 31:12 Do not modify this field. RX FIFO Byte Count Returns the number of bytes currently in the RX FIFO. -

Page 154: Table 12-14: I 2 C Transmit Control Registers 1

MAX32660 User Guide C Transmit Control Register 0 I2Cn_TXCTRL0 [0x0024] Bits Name Access Reset Description TX FIFO Preload Mode Enable 0: Normal operation. An address match in Slave Mode, or a General Call address match, will flush and lock the TX FIFO so it cannot be written and set I2Cn_INTFL0.txloi. -

Page 155: Table 12-15: I C Data Registers

MAX32660 User Guide C Transmit Control Register 1 I2Cn_TXCTRL1 [0x0028] Bits Name Access Reset Description Slave Mode Transmit Last This bit decides what to do if the I C is in Slave Mode, is transmitting data to a Master, and the TX FIFO is empty. -

Page 156: Table 12-17: I C Scl Low Control Register

MAX32660 User Guide C Master Mode Control Register I2Cn_MSTR_MODE [0x0030] Bits Name Access Reset Description Send Repeated START Condition After sending data to a slave, instead of sending a STOP condition the master may send another START to retain control of the bus. -

Page 157: Table 12-20: I C Timeout Registers

MAX32660 User Guide C Timeout Register I2Cn_HS_CLK [0x003C] Bits Name Access Reset Description Hs-Mode Clock High Time This field sets the Hs-Mode clock low count. In Slave mode, this is the time SCL is held low after data is output on SDA. The following equation defined the clock low time. -

Page 158: Table 12-22: I C Dma Register

MAX32660 User Guide C Slave Address Register I2Cn_SLADDR [0x0044] Bits Name Access Reset Description Slave Mode Slave Address When I C peripheral is operating in Slave Mode, I2Cn_CTRL0.mst = 0, this field must be set as the desired slave address for the peripheral. -

Page 159: Figure 13-1: Spi0 Block Diagram

MAX32660 User Guide Serial Peripheral Interface 0 (SPI0) The Serial Peripheral Interface 0 (SPI0) is a highly configurable, synchronous communications peripheral that interfaces to SPI devices and supports both Master and Slave modes. 13.1 SPI Port 0 Features: Four-Wire, full-duplex communication •... -

Page 160: Figure 13-2: 4-Wire Spi Connection Diagram

Slave Select In slave mode, this signal is an input used to indicate the Master is going to start communication. The MAX32660 supports a single slave select pin, SPI0_SS0, for SPI0. A typical four-wire SPI network is shown in Figure 13-2, below. -

Page 161: Figure 13-3: 3-Wire Spi Connection Diagram

13.2.2 Three-Wire SPI Signals Three-wire SPI is supported by the MAX32660 family of microcontrollers. In this variant the MOSI and MISO lines are combined and used as a bi-directional half-duplex communication pin. Three-wire also uses a serial clock generated by the master and a slave select pin controlled by the master. -

Page 162: Table 13-3: Spi0 Pins

The Alternate Function Name column maps the typical SPI Signal name to the Alternate Function name on the MAX32660 family of parts. The required pins for SPI0 are all mapped to Alternate Function 1 on GPIO... -

Page 163: Figure 13-4: Sck Clock Rate Control

MAX32660 User Guide 13.3.4 Three and Four Wire SPI Configuration Select three-wire SPI or four-wire SPI communication using the SPI0_CTRL2.three_wire bit. Set SPI0_CTRL2.three_wire = 0 for four-wire mode or set this bit to 1 to select three-wire operation. 13.3.5 SPI Peripheral Clock The System Peripheral Clock, PCLK, drives the SPI0 peripheral clock. -

Page 164: Figure 13-5: Spi Clock Polarity

MAX32660 User Guide Equation 13-3: SCK Low Time �� = �� × ��������_������_������. ������ ������_������ ������_������ 13.3.7 Clock Phase and Polarity Control SPIn supports four combinations of clock and phase polarity as shown in Table 13-4, below. Clock polarity is controlled using the bit SPI0_CTRL2.clk_pol and determines if the clock is active high or active low as shown in... -

Page 165: Figure 13-6. Spi Timing (Spi0_Ctrl2.Clk_Pha = 0)

MAX32660 User Guide In the case of multi-character transfers with SS0 remaining asserted between characters, the output data will change at the end of the Bit0 (final clock edge) to reflect the output value for Bit15 of the next character. -

Page 166: Figure 13-7. Spi Timing (Spi0_Ctrl2.Clk_Pha = 1)

MAX32660 User Guide Figure 13-7. SPI Timing (SPI0_CTRL2.clk_pha = 1) SCLK (CLKPOL = 0) SCLK (CLKPOL = 1) MOSI Bit15 Bit3 Bit2 Bit1 Bit0 Bit14 MISO Bit15 Bit14 Bit3 Bit2 Bit1 Bit0 Input Sample Time SSEL 13.3.10 Three-Wire SPI Read and Write In three-wire SPI, read and write transactions are controlled using the SPI FIFO enable bits. -

Page 167: Figure 13-8: Three-Wire Spi Read

MAX32660 User Guide Figure 13-8: Three-Wire SPI Read 13.3.10.2 Write Transaction Figure 13-9 shows a three-wire SPI write transaction. The direction is set to write by disabling the receive FIFO (SPI0_DMA.rx_fifo_en = 0) and enabling the transmit FIFO (SPI0_DMA.tx_fifo_en = 1). The SPI0_MOSI(SISO) pin is automatically set as to an output by hardware based on the FIFO enable bits. - Page 168 • Receive FIFO Overrun (Slave Mode only, Master Mode will stall the clock) Note: On the MAX32660 SPI0 use of the Transmit FIFO level interrupt is recommended to avoid the Transmit FIFO empty and the TX FIFO underrun conditions from occurring in both Master or Slave mode operation.

-

Page 169: Table 13-5: Spi0 Master Register Addresses And Descriptions

MAX32660 User Guide SPI0 has four Wakeup (WAKE) sources that can wake the core from SLEEP mode when the WAKE event occurs. The following WAKE events are supported: • Wake on RX FIFO Full • Wake on TX FIFO Empty •... - Page 170 Note: This field is only used when the SPI is configured for Master Mode (SPI0_CTRL0.mm_en = 1). Master Mode Slave Select Output This field must be set to 0 for the MAX32660. 0: Slave Select is an output ss_io 1: Reserved for Future Use Note: This field is only used when the SPI is configured for Master Mode (SPI0_CTRL0.mm_en = 1).

-

Page 171: Table 13-8: Spi Transmit Packet Size Register

MAX32660 User Guide Table 13-8: SPI Transmit Packet Size Register SPI Transmit Packet Size Register SPI0_CTRL1 [0x0008] Bits Name Access Reset Description Number of Receive Characters Number of characters to receive in RX FIFO. Note: If the SPI port is set to operate in 4-wire mode, this field is ignored and the... -

Page 172: Table 13-10: Spi Slave Select Timing Register

MAX32660 User Guide Table 13-10: SPI Slave Select Timing Register SPI Slave Select Timing SPI0_SS_TIME [0x0010] Bits Name Access Reset Description Reserved for Future Use 31:24 Do not modify this field. SS Inactive Clock Delay This is the time SS is inactive, and the bus is inactive between character transmission. -

Page 173: Table 13-12: Spi Dma Control Registers

MAX32660 User Guide SPI Master Clock Configuration Register SPI0_CLK_CFG [0x0014] Bits Name Access Reset Description System Clock to SPI Clock Scale Factor scale Scales the Peripheral Clock (PCLK) by 2 to generate the SPI module clock. �� �������� �� ������_������... -

Page 174: Table 13-13: Spi Interrupt Flag Registers

MAX32660 User Guide SPI DMA Control Register SPI0_DMA [0x001C] Bits Name Access Reset Description RX FIFO Threshold Level When the RX FIFO contains more bytes than the value set in this field, a DMA request is triggered, and the SPI0_INT_FL.rx_level interrupt flag is set. Valid levels for this field are from 0x00 to 0x1E. - Page 175 R/W1C automatically. Note: On the MAX32660 SPI0 port, the SPI0_DMA.tx_fifo_level should be used to avoid an empty TX FIFO condition. TX FIFO Threshold Level Crossed Flag Set when the TX FIFO is less than the value in SPI0_DMA.tx_fifo_level. Write 1 to clear.

-

Page 176: Table 13-14: Spi Interrupt Enable Registers

MAX32660 User Guide Table 13-14: SPI Interrupt Enable Registers SPI Interrupt Enable Register SPI0_INT_EN [0x0024] Bits Name Access Reset Description Reserved for Future Use 31:16 Do not modify this field. RX FIFO Underrun Interrupt Enable rx_und 0: Interrupt is disabled... -

Page 177: Table 13-15: Spi Wakeup Status Flags Registers

MAX32660 User Guide Table 13-15: SPI Wakeup Status Flags Registers SPI Wakeup Status Flags SPI0_WAKE_FL [0x0028] Bits Name Access Reset Description Reserved for Future Use 31:4 Do not modify this field. Wake on RX FIFO Full Flag rx_full R/W1C 0: Wake condition has not occurred. - Page 178 MAX32660 User Guide SPIMSS (SPI1/I 14.1 Overview The SPIMSS peripheral provides either an SPI interface or an I S interface. When set to SPI mode, the peripheral supports SPI with a four-wire full-duplex serial bus operating as either a master or slave. When set to I...

-

Page 179: Figure 14-1. Spimss Block Diagram

MAX32660 User Guide Figure 14-1. SPIMSS Block Diagram An SPI system has a single master and one or more slaves for any given transaction. The SPIMSS supports single master mode networks only when operating in SPI master mode. 14.1.2 Four-Wire SPI Signals SPI devices operate as either a master or slave device. -

Page 180: Figure 14-2: 4-Wire Spi Connection Diagram

MAX32660 User Guide Note: The MAX32660 supports a single slave select pin in the SPIMSS peripheral for SPI1. This pin’s alternate function name is SPI1_SS0. A typical four-wire SPI network is shown in Figure 14-2, below. In a typical SPI network, the master device selects the slave device using the slave select output pin. -

Page 181: Table 14-3: Spimss Pins For Spi1 And I 2 S

The Alternate Function Name column maps the typical SPI signal name to the Alternate Function name on the MAX32660 family of parts. The required pins for SPIMSS are all mapped to Alternate Function 2 on GPIO Port 0 and are... -

Page 182: Table 14-4. Clock Phase And Polarity Operation

MAX32660 User Guide During an SPI transfer, data is sent and received simultaneously by both the master and slave device. When an SPI transfer occurs, a multi-bit character, selectable from 1-bit to 16 bits, is shifted out on the data output line and a multi-bit character is simultaneously shifted in on the data input pin. - Page 183 MAX32660 User Guide 14.3.2.2 SPI Slave Mode When using SPI slave mode, SPIMSS_CTRL.mode = 0, configure the slave select pin, SPI1_SS0, as an input by clearing SPIMSS_CTRL.ss_io. The SPIMSS_MODE.ssv bit is not used in SPI slave mode. 14.3.3 SPI Character Size SPI transmits and receives characters simultaneously.

- Page 184 MAX32660 User Guide The application overhead required to left justify the transmit data can be eliminated by setting the tx_lj bit in the SPIMSS_MODE register. When SPIMSS_MODE.tx_lj = 1, transmit data is always written by software or DMA to SPIMSS_DATA in right justified form and hardware performs the left justify according to SPIMSS_MODE.numbits when the...

- Page 185 MAX32660 User Guide 14.4 S Mode Configure the SPIMSS peripheral for I S mode as follows: • SPIMSS_CTRL.enable = 0, disable the SPIMSS for SPI and I • SPIMSS_I2S_CTRL.i2s_en = 1, enable I S mode • SPIMSS_CTRL.phase = 0, set the phase •...

-

Page 186: Figure 14-3: I S Audio Data In Standard I S Operation

MAX32660 User Guide Figure 14-3: I S Audio Data in Standard I S Operation Figure 14-4: I S Mode (i2s_en=1, i2s_lj=1) 14.5 SPI and I S Error Detection The SPIMSS peripheral includes error detection logic to recognize when communication errors occur for either SPI or I communications. - Page 187 MAX32660 User Guide 14.5.2 SPI Slave Mode Abort A SPI slave mode abort error indicates that the SPI1_SS0 pin deasserted before all bits in a character were transferred. The next time SPI1_SS0 asserts, the SPI1_MISO pin outputs SPIMSS_DATA[15], regardless of where the previous transaction aborted.

- Page 188 MAX32660 User Guide 14.6.4 Bit Rate Generator Time-out Interrupt If the SPI is disabled, an SPI interrupt can be generated by a Bit Rate Generator time-out. This timer function must be enabled by setting the SPIMSS_CTRL.birq bit to 1. 14.7 SPIMSS Bit Rate Generator 14.7.1 SPI and I...

-

Page 189: Table 14-5: Spimss Register Offsets, Access And Descriptions

MAX32660 User Guide Table 14-5: SPIMSS Register Offsets, Access and Descriptions Offset Register Name Access Description [0x0000] SPIMSS_DATA SPIMSS Data Register [0x0004] SPIMSS_CTRL SPIMSS Control Register [0x0008] SPIMSS_INT_FL SPIMSS Interrupt Flag Register [0x000C] SPIMSS_MODE SPIMSS Mode Register [0x0014] SPIMSS_BRG SPIMSS Bit Rate Register... -

Page 190: Table 14-8: Spimss Interrupt Flag Register

MAX32660 User Guide SPIMSS Control Register SPIMSS_CTRL [0x0004] Bits Name Access Reset Description Phase Select Refer to the section 13.3.7 Clock Phase and Polarity Control for details. phase 0: Data is valid prior to first serial clock edge. 1: Data transition occurs after the first serial clock edge. -

Page 191: Table 14-9: Spimss Mode Register

MAX32660 User Guide SPIMSS Interrupt Flag Register SPIMSS_INT_FL [0x0008] Bits Name Access Reset Description Collision Flag This bit is set by hardware when a multi-master collision (mode fault) occurs. Write 1 to clear. R/W1C 0: No multi-master collision has occurred... -

Page 192: Table 14-10: Spimss Bit Rate Generator Register

MAX32660 User Guide SPIMSS Mode Register SPIMSS_MODE [0x000C] Bits Name Access Reset Description Number of Data Bits per Character to Transfer This field contains the number of bits to shift for each character transfer. Refer to the data movement chapter for information on valid bit positions when the character length is less than 16-bits. - Page 193 MAX32660 User Guide SPIMSS DMA Register SPIMSS_DMA [0x0018] Bits Name Access Reset Description Receive FIFO Count 0b0000: RX FIFO empty (0 entries) 0b0001: RX FIFO contains 1 entry 27:24 rx_fifo_cnt 0b0010: RX FIFO contains 2 entries 0b0011: RX FIFO contains 3 entries …...

-

Page 194: Table 14-12: Spimss I 2 S Control Register

MAX32660 User Guide SPIMSS DMA Register SPIMSS_DMA [0x0018] Bits Name Access Reset Description Transmit FIFO Level Sets the TX FIFO DMA request threshold. This configures the number of empty TX FIFO entries before activating a Transmit DMA request. 0b000: Request Transmit DMA when TX FIFO has 1 free entry. - Page 195 Initial Release. 7/18 ©2018 by Maxim Integrated Products, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. MAXIM INTEGRATED PRODUCTS, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT.

Need help?

Do you have a question about the MAX32660 and is the answer not in the manual?

Questions and answers